本发明的一个方式涉及一种晶体管、半导体装置、显示装置及电子设备。此外,本发明的一个方式涉及一种半导体装置的制造方法及显示装置的制造方法。此外,本发明的一个方式涉及一种半导体晶片及模块。注意,在本说明书等中,半导体装置是指能够通过利用半导体特性而工作的所有装置。除了晶体管等的半导体元件之外,半导体电路、运算装置、存储装置也是半导体装置的一个方式。显示装置(液晶显示装置、发光显示装置等)、投影装置、照明装置、电光装置、蓄电装置、存储装置、半导体电路、摄像装置、电子设备等有时包括半导体装置。注意,本发明的一个方式不局限于上述。本说明书等所公开的发明的一个方式涉及一种物体、方法或制造方法。另外,本发明的一个方式涉及一种工序(process)、机器(machine)、产品(manufacture)或者组合物(composition ofmatter)。

背景技术:

1、近年来,已对半导体装置进行开发,lsi、cpu、存储器等主要用于半导体装置。cpu是包括将半导体晶片加工来形成芯片而成的半导体集成电路(至少包括晶体管及存储器)且形成有作为连接端子的电极的半导体元件的集合体。

2、lsi、cpu、存储器等的半导体电路(ic芯片)被安装在电路板上,例如安装在印刷线路板上,并被用作各种电子设备的构件之一。

3、此外,通过使用形成在具有绝缘表面的衬底上的半导体薄膜构成晶体管的技术受到注目。该晶体管被广泛地应用于集成电路(ic)、图像显示装置(简单地记载为显示装置)等电子设备。作为可以应用于晶体管的半导体薄膜,硅类半导体材料被广泛地周知。作为其他材料,氧化物半导体受到关注。

4、另外,已知使用氧化物半导体的晶体管的泄漏电流在非导通状态下极小。例如,专利文献1公开了应用使用氧化物半导体的晶体管的泄漏电流小的特性的低功耗cpu等。另外,例如,专利文献2公开了利用使用氧化物半导体的晶体管的泄漏电流小的特性实现存储内容的长期保持的存储装置等。

5、近年来,随着电子设备的小型化和轻量化,对集成电路的进一步高密度化的要求提高。因此,实现晶体管的微型化的技术被要求。非专利文献1及非专利文献2公开了将硅用于沟道且沟道长度为3nm的没有pn结的晶体管(junctionless-fet)。另外,非专利文献3公开了将氧化物半导体用于沟道且栅极长度为12nm以下的晶体管。

6、[先行技术文献]

7、[专利文献]

8、[专利文献1]日本专利申请公开第2012-257187号公报

9、[专利文献2]日本专利申请公开第2011-151383号公报

10、[非专利文献]

11、[非专利文献1]s.migita,et al,“electrical performances of junctionless-fets atthe scalinglimit(lch=3nm)”,iedm tech.dig.,pp.191-194,2012.

12、[非专利文献2]s.migita,et al,“experimental demonstration ofultrashort-channel(3nm)junctionless fets utilizing atomically sharp v-grooveson soi”,ieee trans.nanotechnol.,13,pp.208-215,2014.

13、[非专利文献3]s.subhechha,et al,“first demonstration of sub-12nm lggate last igzo-tfts with oxygen tunnel architecture for front gate devices”,symposium on vlsi technology digest of technical papers,t10-5,2021.

技术实现思路

1、发明所要解决的技术问题

2、本发明的一个方式的目的之一是提供一种能够实现微型化或高集成化的半导体装置。另外,本发明的一个方式的目的之一是提供一种具有良好的电特性的半导体装置。此外,本发明的一个方式的目的之一是提供一种晶体管的电特性不均匀少的半导体装置。此外,本发明的一个方式的目的之一是提供一种可靠性良好的半导体装置。此外,本发明的一个方式的目的之一是提供一种通态电流大的半导体装置。此外,本发明的一个方式的目的之一是提供一种低功耗的半导体装置。

3、注意,这些目的的记载并不妨碍其他目的的存在。注意,本发明的一个方式并不需要实现所有上述目的。注意,可以从说明书、附图、权利要求书等的记载得知并抽出上述以外的目的。

4、解决技术问题的手段

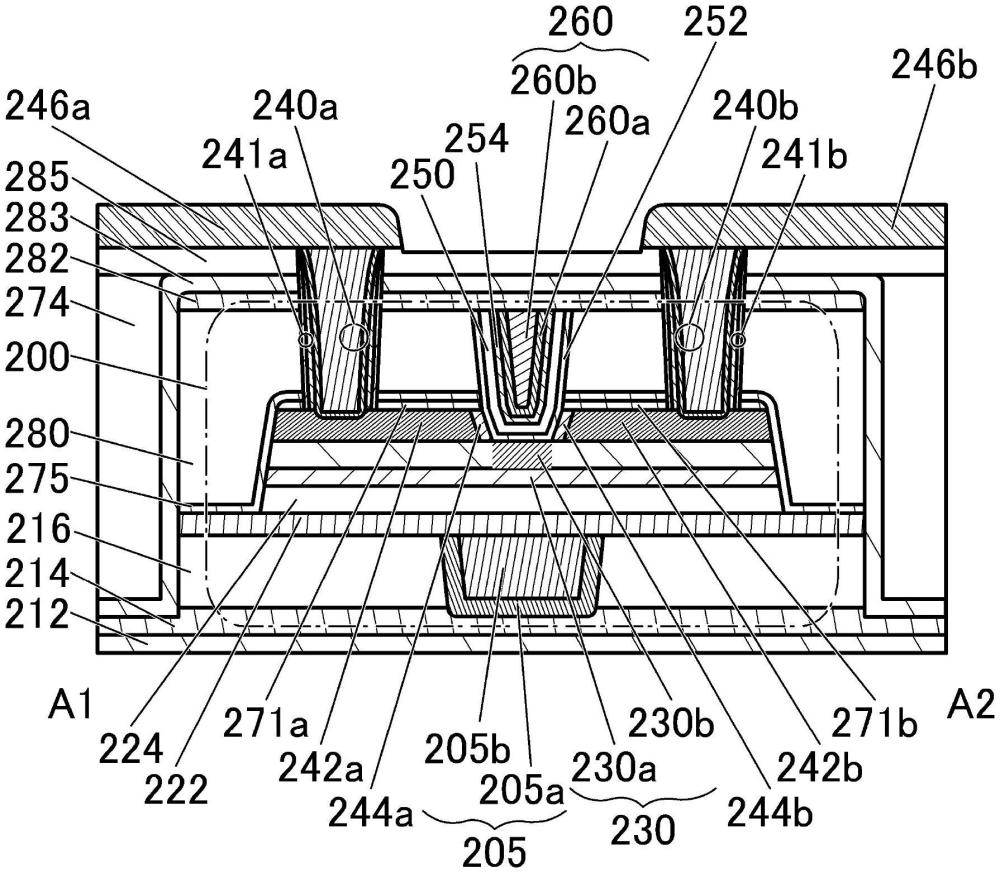

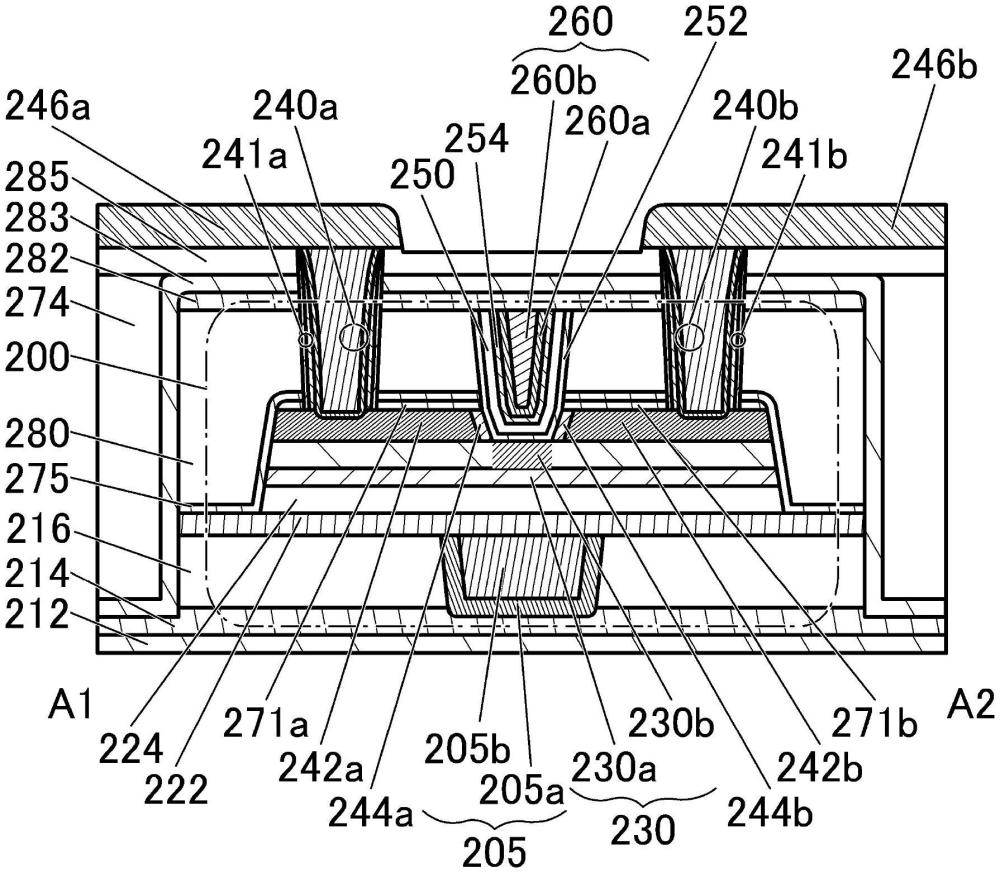

5、本发明的一个方式是一种半导体装置,包括:包括晶体管的沟道形成区域的金属氧化物;金属氧化物上的第一导电体及第二导电体;在金属氧化物上且位于第一导电体与第二导电体间的第一绝缘体;第一绝缘体上的第二绝缘体;第二绝缘体上的第三绝缘体;第三绝缘体上的第三导电体;位于第一导电体与第一绝缘体间的第四绝缘体;位于第二导电体与第一绝缘体间的第五绝缘体;以及位于第一导电体及第二导电体上方的第六绝缘体。第六绝缘体具有开口。开口具有在第一导电体与第二导电体间且重叠于金属氧化物的区域。第一绝缘体、第二绝缘体、第三绝缘体及第三导电体配置在开口内。第一绝缘体具有接触于金属氧化物的顶面的区域、接触于金属氧化物的侧面的区域以及接触于开口的侧壁的区域。第一绝缘体使用与第二绝缘体相比不容易透过氧的材料。第一绝缘体具有膜厚度为1.0nm以上且小于3.0nm的区域。第一导电体及第二导电体都包含金属元素。第四绝缘体及第五绝缘体包含金属元素。在晶体管的沟道长度方向的截面中,从第一导电体到第一绝缘体的距离为第一绝缘体的膜厚度以上且从第三导电体到金属氧化物的距离以下。

6、在上述半导体装置中,优选的是,第一绝缘体使用与第二绝缘体相比不容易透过氧及氢的材料,第三绝缘体使用与第二绝缘体相比不容易透过氢的材料,第一绝缘体及第二绝缘体都包含氧,第二绝缘体及第三绝缘体都包含硅,并且第三绝缘体及第三导电体都包含氮。

7、在上述半导体装置中,第一绝缘体优选包含铝。

8、在上述半导体装置中,金属氧化物优选具有从金属氧化物的底面向金属氧化物的顶面铝浓度变高的浓度梯度。

9、在上述半导体装置中,金属氧化物优选至少包含铟、铝及锌。

10、在上述半导体装置中,金属元素优选为钽或钛。

11、本发明的一个方式是一种半导体装置的制造方法,该半导体装置包括:金属氧化物;第一导电体至第三导电体;第一绝缘体至第四绝缘体;位于第一导电体与第二绝缘体间的第五绝缘体;以及位于第二导电体与第二绝缘体间的第六绝缘体。该半导体装置的制造方法包括如下步骤:依次沉积金属氧化膜、导电膜的第一工序;将金属氧化膜及导电膜加工为岛状而形成金属氧化物及导电层的第二工序;形成第一绝缘体的第三工序;加工第一绝缘体的一部分及导电层的一部分而形成到达金属氧化物的开口、第一导电体以及第二导电体的第四工序;在开口内形成第一绝缘膜的第五工序;在第一绝缘膜上形成第二绝缘膜的第六工序;在含氧气氛下进行微波处理的第七工序;依次沉积第三绝缘膜及第二导电膜的第八工序;以及通过cmp处理形成第二绝缘体、第三绝缘体、第四绝缘体及第三导电体的第九工序。在进行第四工序、第五工序、第六工序及第七工序中的任一个时形成第五绝缘体及第六绝缘体。

12、发明效果

13、根据本发明的一个方式,可以提供一种能够实现微型化或高集成化的半导体装置。此外,根据本发明的一个方式,可以提供一种可靠性良好的半导体装置。另外,根据本发明的一个方式,可以提供一种晶体管的电特性不均匀少的半导体装置。此外,根据本发明的一个方式,可以提供一种具有良好的电特性的半导体装置。另外,根据本发明的一个方式,可以提供一种通态电流大的半导体装置。此外,根据本发明的一个方式,可以提供一种低功耗的半导体装置。

14、注意,这些效果的记载并不妨碍其他效果的存在。注意,本发明的一个方式并不需要具有所有上述效果。注意,可以从说明书、附图、权利要求书等的记载得知并抽出上述以外的效果。