一种高性能ZnSnO薄膜晶体管及其制备方法

本发明主要涉及半导体薄膜晶体管制备,具体涉及一种高性能znsno薄膜晶体管及其制备方法。

背景技术:

1、目前比较主流的氧化物tft通常是基于in2o3半导体的tft器件,但是in元素属于稀缺战略资源,价格昂贵且有毒性,十分不利于环境友好型的可持续性发展理念。基于znsno(zto)半导体材料的薄膜晶体管(tft)由于其成本、环境友好等优点被认为是未来潜在的新型tft器件。然而,目前ztotft器件的电学性能通常较差,无法满足先进显示器件对高分辨率高帧频的显示需求。现有的技术主要可分为以下三种:

2、一是通过元素掺杂来进行调控,但通常某个性能指标的提升会引起其他参数的下降,很难获得综合性能优良的tft器件;例如中国专利申请号为2021100398930的一种znsno薄膜晶体管的制备方法,该技术方案主要是通过制备zto前驱体溶液,将其旋涂在hfo2薄膜上然后将涂覆的薄膜放置在盛有氨水容器上方,具有挥发性nh3扩散到有源层薄膜表面,通过“氨浴”方法实现氮掺杂到zto tft中,可以抑制与氧空位有关的缺陷,提高器件的稳定性;在该技术方案中,虽然阴离子氮掺杂到zto薄膜中可以成功抑制与氧空位有关的缺陷;但实际意义上还是实现场效应迁移率和稳定性之间的折衷选择。

3、二是通过更先进的制备工艺技术,如原子层沉积技术,虽然性能有所提升,但该技术制造成本高,并且与主流工艺也不兼容;例如中国专利申请号为2021101001834的石墨烯导电薄膜的制备方法、以及薄膜晶体管和显示装置,该技术方案就是采用原子层沉积技术在介孔二氧化硅的孔道的内壁面上沉积金属催化层;将沉积金属催化层后的介孔二氧化硅分散在第一有机溶剂中,得到分散液,将分散液制成薄膜;以薄膜为模板,采用化学气相沉积工艺制备石墨烯纳米线,并去除薄膜,得到石墨烯纳米线;将石墨烯纳米线分散至第二有机溶剂中,得到成膜液,将成膜液涂设于基板的表面,得到石墨烯导电薄膜,该制备方法,通过原料的选择和步骤的设计,并充分结合不同工艺的优势,使制得的石墨烯导电薄膜的导电性、透明度和物理性能优良,但该技术制造的材料和工艺成本都很高,不利于产业化应用。

4、三是通过tft器件结构设计,如异质结沟道和双栅结构等,但由于存在一些非理想效应,所能实现的迁移率提升幅度有限。例如中国专利申请号为2022111837993的一种非晶ingazno异质结薄膜晶体管及其制备方法,包括通过磁控溅射方法由下自上依次生长的栅电极、介质层、ingazno前沟道层、源电极、漏电极、ga2o3背沟道层。本发明通过引入非晶态的igzo/ga2o3沟道,利用igzo和ga2o3能带结构的差异,使其形成异质结量子阱传输通道。虽然tft器件性能有所提升,但由于两种材料结构的差异会存在界面质量不佳等非理想效应,进而消弭部分异质结量子阱沟道的优势,导致相对于igzo单层tft器件性能来讲,其提升的幅度十分有限。

5、基于zto半导体的tft器件是未来潜在的电子开关器件,但其性能通常不足以与主流的igzo tft相媲美,严重限制了其自身的应用,目前提高tft器件性能的主流方法中,如上所述均存在技术缺陷,如材料组分优化、先进制备工艺和异质结沟道等,存在着综合性能优化困难、与主流工艺不兼容或者性能提升有限等局限性。

技术实现思路

1、针对上述问题,主要是基于zto半导体的tft器件是未来潜在的电子开关器件,但其性能通常不足以与主流的igzo tft相媲美,严重限制了其自身的应用,目前提高tft器件性能的方法,如材料组分优化、先进制备工艺和异质结沟道等,存在着综合性能优化困难、与主流工艺不兼容或者性能提升有限等局限性,为此,本发明旨在提供一种制备综合性能优良的zto tft的方法,采用同质结策略增强ztotft器件性能的方法,尤指一种高性能znsno薄膜晶体管的制备方法。

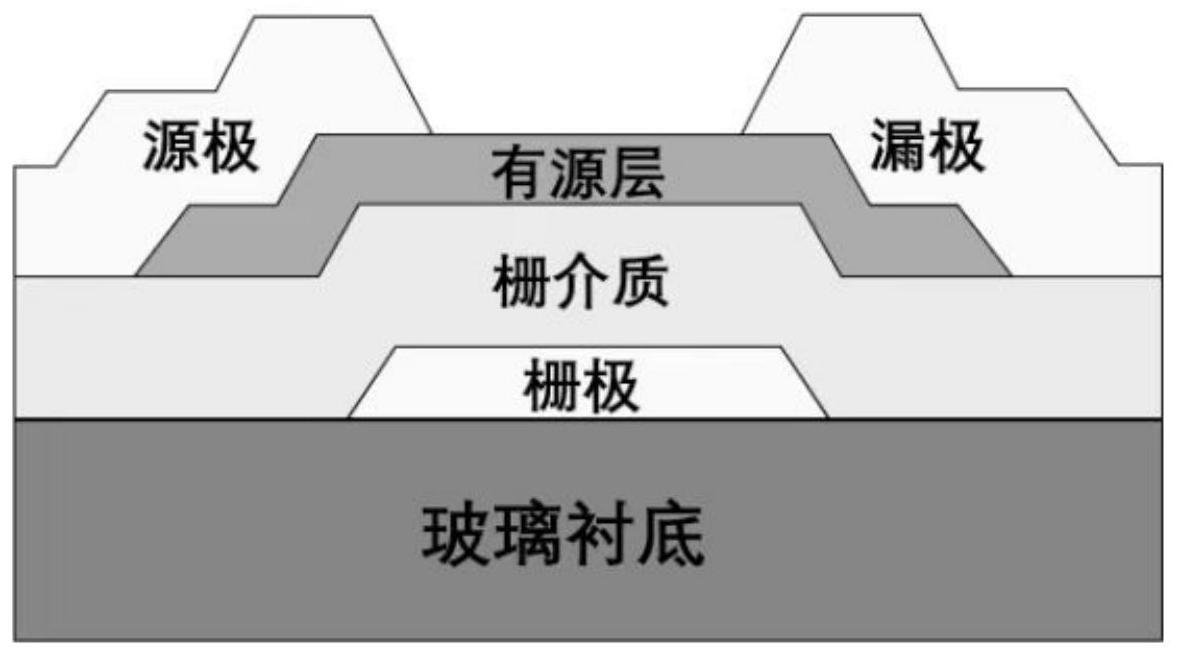

2、本发明解决技术问题所采用的技术方案是:一种高性能znsno薄膜晶体管,所述的薄膜晶体管包括在基板上依次制备生成的栅极、栅介质、有源层和源漏电极,所述的有源层是通过磁控溅射方法制备zto有源层材料,通过控制溅射气氛的氧含量控制氧空位缺陷在有源层中的分布,先沉积富含氧缺陷的zto薄膜,再沉积氧缺陷较少的zto薄膜,使两者的能带结构有所差异,从而形成同质结薄膜;然后通过光刻和刻蚀的工艺进行图形化。

3、一种高性能znsno薄膜晶体管的制备方法,所述的制备方法包括以下步骤:

4、s1、基板预处理:采用玻璃衬底作为基层,并进行超声清洗;

5、s2、制备栅极:采用磁控溅射沉积金属层并图形化形成栅电极;

6、s3、制备栅介质:采用pecvd方法沉积成致密的sio2栅介质层;

7、s4、制备有源层:采用磁控溅射方法制备能带结构差异化的zto有源层材料,形成zto同质结有源层;

8、s5、制备源漏电极:采用磁控溅射方法沉积mo金属层并图形化形成栅电极;

9、s6、薄膜晶体管测试:gate上方栅介质开孔,进行tft器件测试。

10、所述s2中采用磁控溅射方法沉积50nm~150nm厚的mo电极,沉积完成后通过光刻和刻蚀工艺对栅介质层进行图形化。

11、s2中沉积条件为本地真空10-4~10-3pa,直流溅射功率80w~160w,溅射气氛纯ar,工作气压0.3~0.5pa。

12、所述s3中通过pecvd在250℃~350℃条件下沉积一层150nm~250nm厚的sio2栅介质层进行全局覆盖。

13、所述s4中通过控制溅射气氛的氧含量控制氧空位缺陷在有源层中的分布。

14、s4中基本溅射条件为:本地真空10-4pa~10-3pa,交流溅射功率100w~160w,工作气压0.3pa~0.5pa。

15、所述的溅射气氛,先用(20~50)sccm/0sccm的溅射气氛沉积10nm~30nm厚的富含氧缺陷的zto薄膜,再用(20~50)sccm/(1~10)sccm的溅射气氛沉积20nm厚氧缺陷较少的zto薄膜,从而形成同质结薄膜;紧接着在250℃~400℃真空条件下退火0.5~2个小时,然后通过光刻和刻蚀的工艺进行图形化。

16、所述的s5中,通过光刻和剥离工艺沉积和图形化mo源漏电极。

17、所述s6中,将全局覆盖的sio2栅介质局部进行开孔以暴露底栅电极。

18、所述sio2栅介质开孔采用光刻图形化和反应离子刻蚀的方法

19、本发明达到的技术效果是:本发明的技术方案,成功克服了目前主流技术中存在的不足,首先,本发明通过控制氧空位的分布制备同质结,制备方法简单可控;其次,本发明通过同质结的策略提升tft器件性能,能减少界面散射,最大限度发挥量子阱的正面效应;再次,本发明的整个制备过程,与主流产业化工艺高度兼容,可以直接转化应用;更重要的是,本发明的技术与主流的igzo tft性能相媲美,升级换代后可降低tft显示背板的制造成本;该方法也适用于其他氧化物半导体材料与电子器件,具有较强的可推广性。

- 还没有人留言评论。精彩留言会获得点赞!