半导体结构及其形成方法、图像传感器与流程

本发明涉及半导体,尤其涉及一种半导体结构、一种半导体结构的形成方法以及一种图像传感器。

背景技术:

1、由堆叠的下极板、介电层、上极板构成的mim(metal-insulator-metal)电容具有q值较高、耐压性能佳以及低esr(等效串联电阻)等特性,并且与集成电路的工艺兼容性较好,目前在半导体装置中被广泛应用。

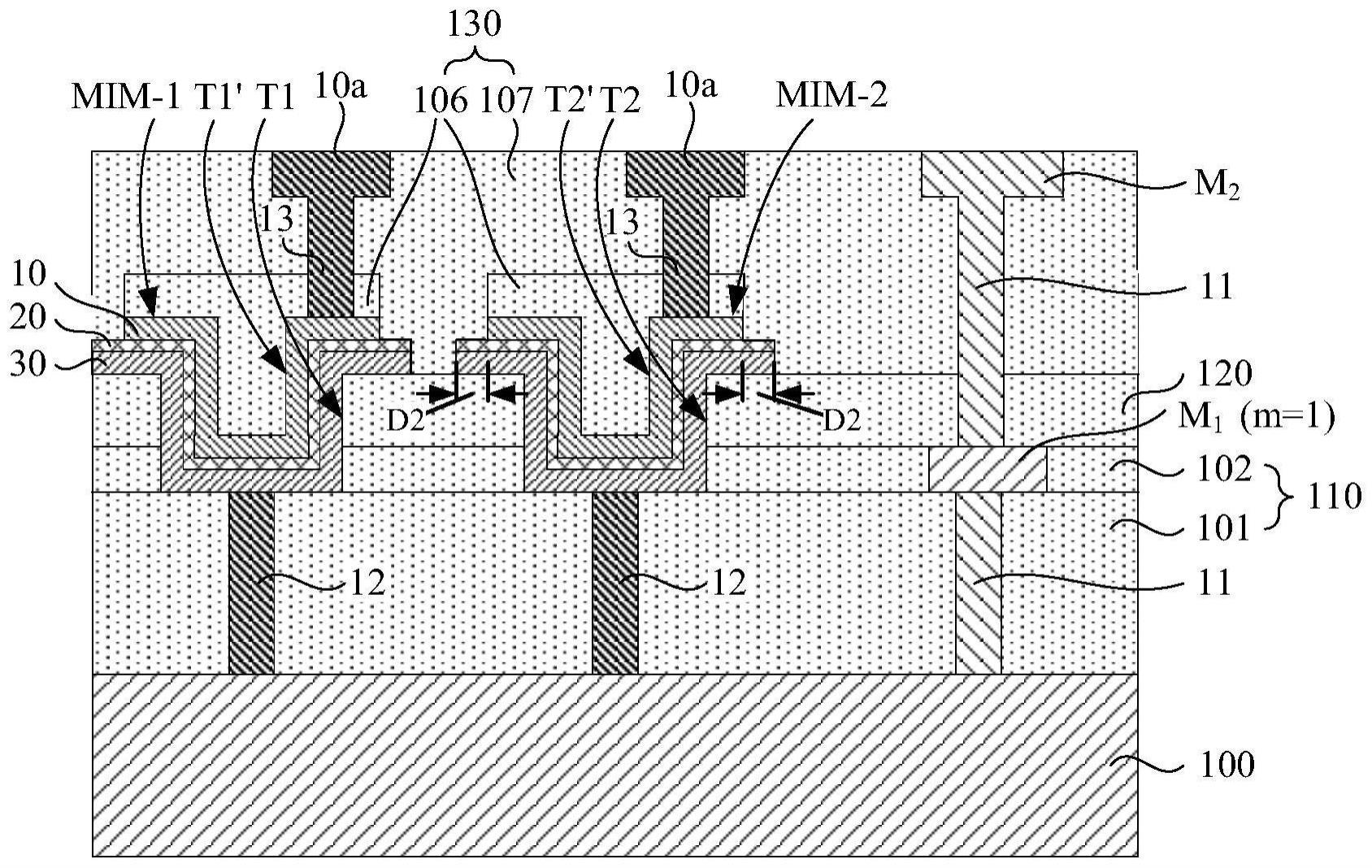

2、图1是一种现有的具有mim电容的半导体装置的局部剖面示意图。参照图1,现有工艺在两个互连金属层之间制作mim电容,其中,在形成位于下方的互连金属层mx之后,沉积介质材料,再在介质材料表面覆盖下极板材料层、介电材料层以及上极板材料层的叠层,之后对该叠层进行图形化,形成上极板10、介电层20和下极板30,之后再沉积介质材料,并在mim电容的上极板10一侧形成分别连接所述上极板10和下极板30的插塞以及位于上方的互连金属层mx+1。

3、上述制作工艺至少存在如下问题:

4、首先,上述mim电容的电容值通常采用上极板10的面积进行估算,但是,为了确保分别连接上极板10和下极板30的插塞的可靠性,避免mim电容在与极板平行的二维平面内占据的面积过大,上极板10的面积即mim电容的有效面积受到限制,不利于增大mim电容的电容值;

5、其次,为了避免串扰,半导体装置中的其它电性组件需避免设置于mim电容的下极板30下方,进一步限制了半导体装置的设计灵活性;

6、其次,在对下极板材料层、介电材料层以及上极板材料层的叠层进行图形化时,需通过曝光工艺定义上极板10、介电层20以及下极板30的范围,但是,由于位于该叠层下方的对准标记被该叠层覆盖且该叠层的透光性差,对准操作造成影响,为了解决该问题,一种现有方案在介质材料表面形成所述叠层之前,在mim电容的形成区域以外形成一对准沟槽40,在形成所述叠层时,使所述叠层保形覆盖所述对准沟槽40,从而在所述对准沟槽40处形成由所述叠层围成的保形沟槽,在对所述叠层进行图形化时,曝光机可以检测出所述保形沟槽的图形,从而可以利用所述保形沟槽的图形作为对准标记进行相应的曝光工艺,但是,在制作所述mim电容之前额外增加对准沟槽40的制作导致晶圆流片时间延长,降低了流片效率,存在产能浪费的问题;

7、此外,由于较靠近半导体衬底的金属互连层通常线条密度较大,为了容纳mim电容,通常在半导体衬底上方形成两层、三层或者四层互连金属层后再利用上述工艺制作mim电容,为此,半导体装置中除了需设置连接mim电容外的其它电子元器件的互连金属层,一些情况下还需额外增加互连金属层以容纳mim电容,容易导致半导体装置的整体厚度较大,制作成本提高。

技术实现思路

1、为了解决上述现有技术存在的问题,本发明提供一种半导体结构、一种半导体结构的形成方法以及一种图像传感器。

2、一方面,本发明提供一种半导体结构,所述半导体结构包括:

3、前端器件结构;

4、堆叠于所述前端器件结构上的n个金属互连层,所述前端器件结构以及n个所述金属互连层之间通过介质材料隔离并通过形成于所述介质材料内的多个导电插塞互连;以及

5、至少一沟槽型mim电容,嵌入沿远离所述前端器件结构的方向的第m金属互连层的平面且与所述第m金属互连层通过所述介质材料隔离,m和n均为整数且1≦m≦n。

6、另一方面,本发明提供一种半导体结构的形成方法,所述形成方法包括:

7、提供一前端器件结构;以及

8、在所述前端器件结构上形成n个金属互连层以及至少一沟槽型mim电容,所述前端器件结构以及n个所述金属互连层之间通过介质材料隔离并通过形成于所述介质材料内的多个导电插塞互连,至少一所述沟槽型mim电容嵌入沿远离所述前端器件结构的方向的第m金属互连层的平面且与所述第m金属互连层通过所述介质材料隔离,m和n均为整数且1≦m≦n。

9、再一方面,本发明提供一种图像传感器,所述图像传感器包括:

10、器件基底,所述器件基底中形成有光电二极管和浮置扩散区,所述浮置扩散区域用于接收来自所述光电二极管的光生电荷;

11、堆叠于所述器件基底上的n个金属互连层,所述器件基底以及n个所述金属互连层之间通过介质材料隔离并通过形成于所述介质材料内的多个导电插塞互连;以及

12、至少一沟槽型mim电容,嵌入沿远离所述器件基底的方向的第m金属互连层的平面且与所述第m金属互连层通过所述介质材料隔离,m和n均为整数且1≦m≦n,所述沟槽型mim电容与所述浮置扩散区耦接。

13、本发明提供的半导体结构中,金属互连层和沟槽型mim电容形成于前端器件结构上方,并且,所述沟槽型mim电容嵌入沿远离所述前端器件结构的方向的第m金属互连层的平面且与所述第m金属互连层通过介质材料隔离,所述沟槽型mim电容具有下凹的曲面形状,相对于平面形状的电容,有助于增加电容的有效面积和电容值,缩小电容在半导体结构中占据的面积,提高半导体结构的设计灵活性;用于形成所述沟槽型mim电容的叠层材料所围成的保形沟槽可作为一些曝光工艺中的对准标记,如此可省去专门制作相应曝光工艺的对准标记的工序,有助于提高流片效率,降低成本。进一步地,可使沟槽型mim电容的上极板和下极板分别从所述沟槽型mim电容的上下两侧引出,有助于进一步缩小沟槽型mim电容所占的面积,提高半导体结构的设计灵活性,并且,由于沟槽型mim电容占据的面积较小,其在前端器件结构上的位置设置较灵活,更便于容纳,不需要额外增加互连金属层的数量,例如可以嵌入较靠近前端器件结构的金属互连层的平面(例如第一金属互连层m1所在平面),有助于降低成本。

14、本发明提供的半导体结构的形成方法中,在前端器件结构上形成n个金属互连层以及至少一沟槽型mim电容,至少一所述沟槽型mim电容嵌入沿远离所述前端器件结构的方向的第m金属互连层的平面且与所述第m金属互连层通过介质材料隔离。所述沟槽型mim电容的有效面积和电容值较平面形状的电容更便于增大,而占据面积较小,有助于提高半导体结构的设计灵活性。用于形成所述沟槽型mim电容的叠层材料所围成的保形沟槽可作为一些曝光工艺(如刻蚀该叠层材料以形成所述沟槽型mim电容的曝光工艺)中的对准标记,如此可省去专门制作对准标记的工序,有助于提高流片效率,降低成本。进一步地,在制作所述沟槽型mim电容时,可结合光阻掩模刻蚀工艺、自对准刻蚀工艺以及修整工艺,使所形成的沟槽型mim电容中的下极板和介电层的端部相对于同一方向上的上极板的端部更远离所述沟槽,不仅节约光罩,而且能够降低所述上极板与所述下极板之间形成短路连接的风险。

15、本发明提供的图像传感器包括器件基底、堆叠于所述器件基底上的n个金属互连层以及至少一沟槽型mim电容,所述沟槽型mim电容嵌入沿远离所述器件基底的方向的第m金属互连层的平面且与所述第m金属互连层通过所述介质材料隔离,所述沟槽型mim电容具有下凹的曲面形状,有助于增大电容值,缩小占据面积,并且,用于形成所述沟槽型mim电容的叠层材料所围成的保形沟槽可作为一些曝光工艺中的对准标记,如此可省去专门制作相应曝光工艺的对准标记的工序,有助于提高图像传感器的流片效率,降低成本。

- 还没有人留言评论。精彩留言会获得点赞!