半导体装置和半导体装置的制造方法与流程

本发明涉及半导体,尤其是涉及一种半导体装置和半导体装置的制造方法。

背景技术:

1、rc-igbt(逆导型绝缘栅型双极晶体管reverse conducting-insulated gatebipolar transistor)是指在单个芯片上集成了igbt(绝缘栅型双极晶体管insulatedgate bipolar transistor)和frd(快恢复二极管fast recovery diode)。一般而言,行业中通常将igbt和frd通过集总式或分布式的方法,集成在芯片的元胞区,二者共用终端,从而实现了集成度较高的rc-igbt,无需再通过封装将igbt和frd两个分立器件连接起来。

2、在相关技术中,rc-igbt的结构设计不够合理,frd在由导通状态转变为关断状态的过程里,其内部存储的非平衡载流子会被释放出来,从而产生一个较大的反向恢复电流,并导致较大的开关损耗。另外,当frd发生动态雪崩,局部集中的电流可能会使薄弱区域发生烧毁,进而损坏器件。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明的一个目的在于提出一种半导体装置,该半导体装置的工作性能更佳。

2、本发明的另一个目的在于提出一种半导体装置的制造方法。

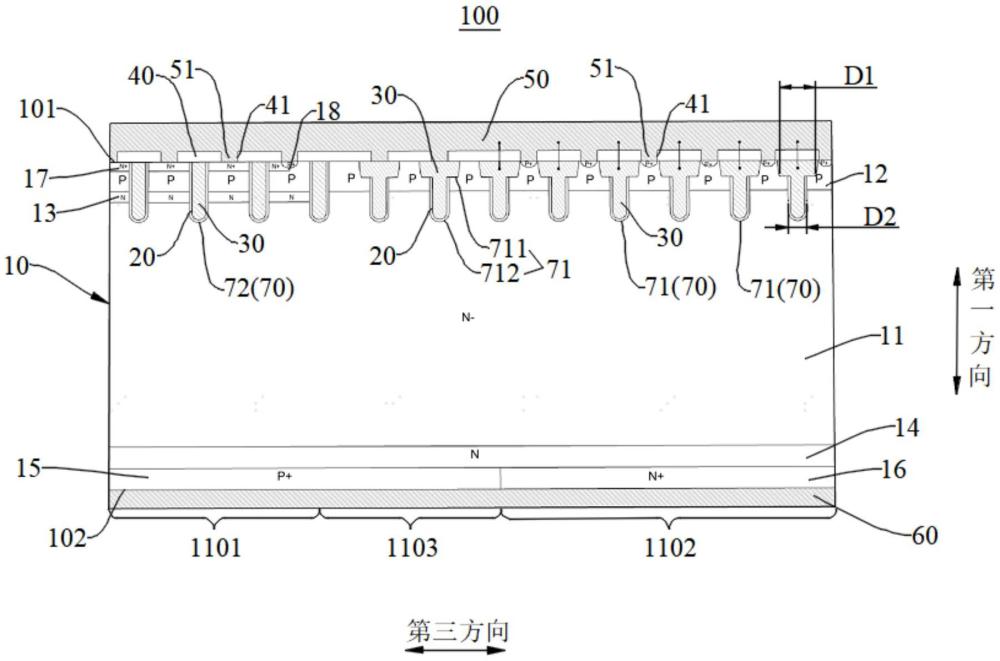

3、根据本发明实施例的半导体装置,包括:基体,所述基体具有第一主面及与第一主面相反侧的第二主面,所述第一主面和所述第二主面在第一方向上间隔设置;第一导电类型的漂移层,所述漂移层设置于所述基体且位于第一主面和第二主面之间;第二导电类型的基极层,所述基极层设置于所述漂移层朝向所述第一主面的一侧,所述基极层的上表面构成所述第一主面的一部分,所述基极层厚度从所述第一主面沿第一方向朝向第二主面延伸设置;沟槽,所述沟槽厚度方向上从所述第一主面将所述基极层贯穿而到达所述漂移层,所述沟槽的长度方向在所述半导体装置的第二方向上延伸,所述沟槽为多个,多个所述沟槽在所述半导体装置的第三方向上间隔设置,其中,所述第一方向、所述第二方向和所述第三方向相互垂直;氧化层,所述半导体装置具有快恢复二极管区域和绝缘栅双极晶体管区域,所述绝缘栅双极晶体管区域周向环绕设置于所述快恢复二极管区域的外侧,多个所述沟槽包括多个第一沟槽和多个第二沟槽,所述快恢复二极管区域中设置有多个所述第一沟槽,所述绝缘栅双极晶体管区域中设置有多个所述第二沟槽,所述第一沟槽包括第一沟槽部和第二沟槽部,所述第一沟槽部位于所述第二沟槽部更加靠近所述第一主面的一侧,所述氧化层设置于所述第二沟槽部的内壁;第一导电类型的多晶硅,所述多晶硅设置于所述第一沟槽内,所述第二沟槽部内壁的所述氧化层将所述第二沟槽部中的所述多晶硅与所述基极层隔开,所述第一沟槽部中的所述多晶硅与所述基极层相接触;介质层,所述介质层设置于所述第一主面;发射极金属层,所述发射极金属层设置于所述介质层远离所述第一主面的一侧,所述发射极金属层至少部分地穿过所述介质层与所述基极层相接触,所述发射极金属层与所述多晶硅电连接。

4、由此,通过对快恢复二极管区域的第一沟槽进行优化,使氧化层仅设置于第一沟槽的第二沟槽部的内壁,第一沟槽部中的多晶硅与基极层相接触,发射极金属层至少部分地与多晶硅电连接,这样在不影响半导体装置的正常工作的前提下,使载流子可以在第一沟槽部中的多晶硅与基极层之间流动,从而提高快恢复二极管区域正向导通中的空穴注入效率,以及提高快恢复二极管区域反向恢复时的空穴抽取效率,进而可以进一步地提高动态雪崩耐量,以及降低反向恢复电流、减少反向恢复时间,进一步地提升半导体装置的工作性能。

5、在本发明的一些示例中,所述第一沟槽部第三方向的宽度大于所述第二沟槽部第三方向的宽度。

6、在本发明的一些示例中,所述第一沟槽部第三方向的宽度为d1,所述第二沟槽部第三方向的宽度为d2,d1和d2满足关系式:d2<d1<2.5d2。

7、在本发明的一些示例中,所述第一沟槽部第一方向的厚度小于所述第二沟槽部第一方向的厚度。

8、在本发明的一些示例中,所述半导体装置还包括过渡区域,所述过渡区域周向环绕设置于所述快恢复二极管区域的外侧,所述过渡区域位于所述快恢复二极管区域和所述绝缘栅双极晶体管区域之间,所述过渡区域也设置有多个所述第一沟槽。

9、在本发明的一些示例中,所述半导体装置还包括连接沟槽,所述连接沟槽厚度方向上从所述第一主面将所述基极层贯穿而到达所述漂移层,所述连接沟槽的长度方向在所述半导体装置的第三方向上延伸,所述连接沟槽位于多个所述第一沟槽第二方向的端部且与多个所述第一沟槽第二方向的端部均相互连通,所述多晶硅设置于所述连接沟槽内,所述连接沟槽中的所述多晶硅与所述第一沟槽中的所述多晶硅相接触,所述发射极金属层至少部分地穿设所述介质层且与所述连接沟槽中的所述多晶硅相接触。

10、在本发明的一些示例中,所述连接沟槽包括第三沟槽部和第四沟槽部,所述第三沟槽部位于所述第四沟槽部更加靠近所述第一主面的一侧,所述第四沟槽部的内壁设置有所述氧化层,所述第四沟槽部内壁的所述氧化层将所述第四沟槽部中的所述多晶硅与所述基极层隔开,所述第三沟槽部中的所述多晶硅与所述基极层相接触。

11、在本发明的一些示例中,所述连接沟槽为两个,两个所述连接沟槽分别位于多个所述第一沟槽第二方向的两端,两个所述连接沟槽分别将多个所述第一沟槽第二方向的两端相互连通。

12、在本发明的一些示例中,所述介质层对应相邻两个所述第一沟槽之间的部分设置有第一穿孔,所述发射极金属层上设置有第一连接凸起,所述第一连接凸起穿设所述第一穿孔且与所述基极层接触连接;所述介质层对应所述连接沟槽的部分设置有第二穿孔,所述发射极金属层上设置有第二连接凸起,所述第二连接凸起穿设所述第二穿孔且与所述多晶硅接触连接。

13、根据本发明实施例的半导体装置的制造方法用于制造以上所述的半导体装置,所述半导体装置的制造方法包括以下步骤:制备基体,在所述基体内注入形成第二导电类型的集电极层、第一导电类型的场截止层、第一导电类型的漂移层、第一导电类型的载流子存储层、第二导电类型的基极层;在所述基体中刻蚀第一沟槽、第二沟槽和连接沟槽,并在所述第一沟槽、所述第二沟槽、所述连接沟槽和所述基体的表面生长氧化层;通过光刻及蚀刻氧化层和基体,以使第一沟槽包括第一沟槽部和第二沟槽部,使连接沟槽包括第三沟槽部和第四沟槽部;沉积第一导电类型的多晶硅,并对所述多晶硅进行刻蚀。

14、在本发明的一些示例中,沉积第一导电类型的多晶硅,并对所述多晶硅进行刻蚀的步骤之后,所述半导体装置的制造方法还可以包括:在所述基极层对应所述第二沟槽的两侧注入第一导电类型掺杂剂,形成发射层;在所述氧化层和所述多晶硅的表面沉积介质层;在所述介质层表面刻蚀第一穿孔和第二穿孔,或在介质层表面刻蚀第一穿孔和第三穿孔;沉积发射极金属层;在集电极层中注入形成第一导电类型掺杂剂,形成阴极层;在第二主面上沉积集电极金属层。

15、本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!