功率子模组及具有其的功率模块的制作方法

本发明涉及功率器件,具体而言,涉及一种功率子模组及具有其的功率模块。

背景技术:

1、全控型器件功率场效应晶体管(mosfet)是一种半导体器件,它属于电压控制型器件,使用栅极电压来控制电流的流动。mosfet是金属-氧化物-半导体(mos)结构的场效应晶体管,广泛应用于各种电子电路中,尤其是在功率电子领域。全控型器件功率场效应晶体管(mosfet),凭借其输入阻抗高、开关速率快、驱动要求低等优点,被认为是理想的开关器件。但是传统硅基功率mosfet器件在高压领域的功率处理能力受到芯片内阻的限制,如何降低芯片导通电阻,提高芯片击穿电压,是下一代功率mosfet器件的研究重点。

2、在相关技术中,以碳化硅材料为代表的宽禁带半导体材料,以其优良的材料特性:宽的禁带宽度,高的临界击穿场强,高的饱和载流子迁移率,被认为是下一代高压功率器件的理想材料。在所有的碳化硅器件中,碳化硅mosfet具有导通电阻低、开关速度快、耐受电压高等优点,已经逐渐替代硅基mosfet和igbt器件。由于单颗芯片的电流等级较低,在大电流应用下,一般采用多颗芯片并联封装成功率模块。目前,碳化硅功率模块的封装依旧采用传统的硅基功率模块的封装,功率模块的寄生电感较大,而碳化硅的开关速度快,较大的寄生电感在开关瞬态产生较大的电压过冲,严重限制了碳化硅器件在高压领域的应用,无法充分发挥碳化硅耐受电压高的优势。

3、因此,相关技术中存在功率模块的寄生电感较大,限制了碳化硅器件在高压领域的应用的问题。

技术实现思路

1、本发明提供一种功率子模组及具有其的功率模块,以解决相关技术中的功率模块的寄生电感较大,限制了碳化硅器件在高压领域的应用的问题。

2、根据本发明的一个方面,提供了一种功率子模组,功率子模组包括:上半桥单元,包括上基板、多个并联的上mosfet芯片、上串联二极管以及多个并联的上二极管芯片,上mosfet芯片的数量为偶数,且两个上mosfet芯片为一个上mosfet芯片组,两个上mosfet芯片组之间设置有一个上串联二极管,上mosfet芯片的漏极与上基板的第一上漏极导电层连接,上mosfet芯片的功率源极与上二极管芯片的阳极连接,上串联二极管的阴极与第一上漏极导电层连接,上串联二极管的阳极与上基板的第二上漏极导电层连接,上二极管芯片的阴极与第二上漏极导电层连接,上二极管芯片的阳极与上基板的上功率源极导电层连接;下半桥单元,包括下基板、多个并联的下mosfet芯片、下串联二极管以及多个并联的下二极管芯片,下mosfet芯片的数量为偶数,且两个下mosfet芯片为一个下mosfet芯片组,两个下mosfet芯片组之间设置有一个下串联二极管,下mosfet芯片的漏极与下基板的第一下漏极导电层连接,下mosfet芯片的功率源极与下二极管芯片的阳极连接,下串联二极管的阴极与第一下漏极导电层连接,下串联二极管的阳极与下基板的第二下漏极导电层连接,下二极管芯片的阴极与第二下漏极导电层连接,下二极管芯片的阳极与下基板的下功率源极导电层连接,上功率源极导电层与第二下漏极导电层连接。

3、进一步地,上半桥单元还包括上漏极功率端子,上漏极功率端子与第二上漏极导电层连接;下半桥单元还包括第一下输出功率端子、第二下输出功率端子以及下功率源极功率端子,下功率源极功率端子与下功率源极导电层连接,第一下输出功率端子和第二下输出功率端子分别与第二下漏极导电层连接。

4、进一步地,上漏极功率端子、第一下输出功率端子、第二下输出功率端子以及下功率源极功率端子均为低螺纹功率端子。

5、进一步地,上基板上设置有两个上功率源极导电层,两个上功率源极导电层分别设置在上漏极功率端子的两侧;第二下漏极导电层包括第一段、第二段以及第三段,第一段和第三段分别与第二段的两端连接,第一段和第三段位于第二段的同一侧,多个下二极管芯片沿第二段的延伸方向间隔设置在第二段上,第二下输出功率端子设置在第一段上,第一下输出功率端子设置在第三段上;第一段与其中一个上功率源极导电层连接,第三段与另一个上功率源极导电层连接。

6、进一步地,第二上漏极导电层包括相垂直的第四段和第五段,第五段的一端与第四段的中部连接,多个上二极管芯片沿第四段的长度方向间隔设置在第四段上,上漏极功率端子设置在第五段上。

7、进一步地,第一段通过第一桥臂连接键合线与其中一个上功率源极导电层连接,第三段通过第二桥臂连接键合线与另一个上功率源极导电层连接。

8、进一步地,上mosfet芯片的栅极与上基板的第一上栅极导电层连接,上mosfet芯片的驱动源极与上基板的上驱动源极导电层连接,上半桥单元还包括上驱动电阻、第一上栅极信号端子、第一上驱动源极信号端子、第二上驱动源极信号端子以及第二上栅极信号端子,第一上栅极导电层与上驱动电阻连接,上驱动电阻与上基板的第二上栅极导电层连接,第一上栅极信号端子和第二上栅极信号端子分别与第二上栅极导电层连接,第一上驱动源极信号端子和第二上驱动源极信号端子分别与上驱动源极导电层连接;下mosfet芯片的栅极与下基板的第一下栅极导电层连接,下mosfet芯片的驱动源极与下基板的下驱动源极导电层连接,下半桥单元还包括下驱动电阻、第一下驱动源极信号端子、第一下栅极信号端子、第二下驱动源极信号端子以及第二下栅极信号端子,第一下栅极导电层与下驱动电阻连接,下驱动电阻与下基板的第二下栅极导电层连接,第一下栅极信号端子和第二下栅极信号端子分别与第二下栅极导电层连接,第一下驱动源极信号端子和第二下驱动源极信号端子分别与下驱动源极导电层连接。

9、进一步地,第一上漏极导电层位于第二上漏极导电层远离上功率源极导电层的一侧,多个上mosfet芯片沿第一上漏极导电层的长度方向间隔排布,上半桥单元包括多个上驱动电阻,上基板上设置有多个第一上栅极导电层,多个第一上栅极导电层与多个上mosfet芯片一一对应设置,多个上驱动电阻与多个第一上栅极导电层一一对应设置,多个第一上栅极导电层均位于第一上漏极导电层远离第二上漏极导电层的一侧,第二上栅极导电层位于第一上栅极导电层远离第一上漏极导电层的一侧,上驱动源极导电层位于第二上栅极导电层远离第一上栅极导电层的一侧;第一下漏极导电层位于第二下漏极导电层的远离下功率源极导电层的一侧,下半桥单元包括多个下驱动电阻,下基板上设置有多个第一下栅极导电层,多个第一下栅极导电层与多个下mosfet芯片一一对应设置,多个下驱动电阻与多个第一下栅极导电层一一对应设置,多个第一下栅极导电层均位于第一下漏极导电层的远离第二下漏极导电层一侧,第二下栅极导电层位于第一下栅极导电层的远离第一下漏极导电层的一侧,下驱动源极导电层位于第二下栅极导电层的远离第一下栅极导电层的一侧。

10、进一步地,第一上漏极导电层、第二上栅极导电层以及上驱动源极导电层均为长条状结构;第一下漏极导电层、第二下栅极导电层以及下驱动源极导电层均为长条状结构。

11、进一步地,上mosfet芯片的漏极通过焊料与第一上漏极导电层烧结连接,上mosfet芯片的功率源极通过第一上mosfet功率源极键合线与上二极管芯片的阳极连接,上mosfet芯片的栅极通过上mosfet栅极键合线与第一上栅极导电层连接,上mosfet芯片的驱动源极通过上mosfet驱动源极键合线与上驱动源极导电层连接,上串联二极管的阴极通过焊料与第一上漏极导电层烧结连接,上串联二极管的阳极通过上串联二极管阳极键合线与第二上漏极导电层连接,上二极管芯片的阴极通过焊料与第二上漏极导电层烧结连接,上二极管芯片的阳极通过第二上mosfet功率源极键合线与上功率源极导电层连接;下mosfet芯片的漏极通过焊料与第一下漏极导电层烧结连接,下mosfet芯片的功率源极通过第一下mosfet功率源极键合线与下二极管芯片的阳极连接,下mosfet芯片的栅极通过下mosfet栅极键合线与第一下栅极导电层连接,下mosfet芯片的驱动源极通过下mosfet驱动源极键合线与下驱动源极导电层连接,下串联二极管的阴极通过焊料与第一下漏极导电层烧结连接,下串联二极管的阳极通过下串联二极管阳极键合线与第二下漏极导电层连接,下二极管芯片的阴极通过焊料与第二下漏极导电层烧结连接,下二极管芯片的阳极通过第二下mosfet功率源极键合线与下功率源极导电层连接,上功率源极导电层与第二下漏极导电层连接。

12、进一步地,上半桥单元包括四个并联的上mosfet芯片、一个上串联二极管以及三个并联的上二极管芯片;下半桥单元包括四个并联的下mosfet芯片、一个下串联二极管以及三个并联的下二极管芯片。

13、进一步地,上基板和下基板均为陶瓷基板。

14、根据本发明的另一方面,提供了一种功率模块,功率模块包括:基板;功率子模组,设置在基板上,功率子模组为上述提供的功率子模组。

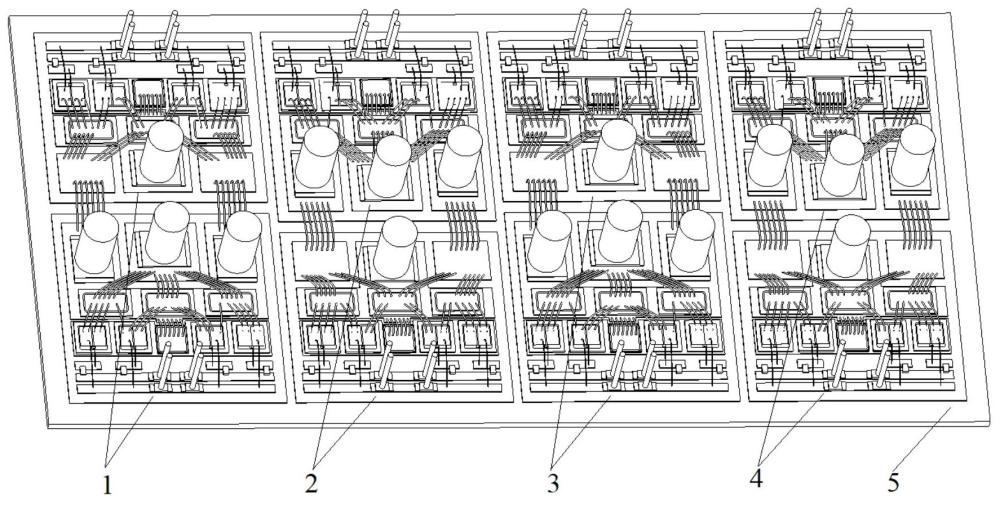

15、进一步地,功率模块包括多个功率子模组。

16、进一步地,多个功率子模组在基板的长度方向上间隔排布,每个功率子模组的上半桥单元和下半桥单元在基板的宽度方向上间隔排布。

17、进一步地,相邻两个功率子模组的电流流向相反。

18、进一步地,功率子模组的上基板的下表面与基板通过焊料烧结连接,功率子模组的下基板的下表面与基板通过焊料烧结连接。

19、应用本发明的技术方案,该功率子模组包括上半桥单元和下半桥单元,上半桥单元包括上基板、多个并联的上mosfet芯片、上串联二极管以及多个并联的上二极管芯片,上mosfet芯片的数量为偶数,且两个上mosfet芯片为一个上mosfet芯片组,两个上mosfet芯片组之间设置有一个上串联二极管。下半桥单元包括下基板、多个并联的下mosfet芯片、下串联二极管以及多个并联的下二极管芯片,下mosfet芯片的数量为偶数,且两个下mosfet芯片为一个下mosfet芯片组,两个下mosfet芯片组之间设置有一个下串联二极管。采用上述结构,上串联二极管可以对多个并联的上mosfet芯片进行分组,下串联二极管可以对多个并联的下mosfet芯片进行分组,消除了电流耦合效应。

- 还没有人留言评论。精彩留言会获得点赞!