一种ESD保护电路、检波电路及相关电子装置的制作方法

一种esd保护电路、检波电路及相关电子装置

技术领域

1.本技术涉及一种电路,尤其涉及一种esd保护电路、检波电路及相关电子装置。

背景技术:

2.现代电子传感技术中,经常使用检波电路对传感器产生的波信号的幅度进行检测,以达到感测变量的目的。而由于传感器的感应极板通常裸露在外面,在晶圆制造以及后续封装、再加工流程中容易遭受静电损坏,导致芯片电路(例如检波电路)损毁,影响检波电路的检测性能,会降低芯片良率。

3.现有的技术中通常需要额外加入二极管、ggnmos(gate-grounded nmos,栅接地n型晶体管)或者gdpmos(gate-to-drain pmos,栅极接漏极p型晶体管)等器件来作为esd(electro-static discharge,静电释放)保护电路,但是这种esd保护电路的面积较大,会引入较大的寄生电容,从而分走一部分信号量,影响检波电路的检测结果准确性。

技术实现要素:

4.本技术提供一种esd保护电路、检波电路和相关电子装置,能够有效解决现有的检波电路中需额外引入其他器件的问题。

5.第一方面,提供了一种esd保护电路,包括窗口选择开关,所述窗口选择开关具有两个寄生二极管,其中一个所述寄生二极管的负极与所述检波电路的电源耦接,另一个所述寄生二极管的正极接地,所述一个寄生二极管的正极与所述另一个寄生二极管的负极耦接。

6.在一些可能的实现方式中,所述窗口选择开关包括第一开关和第二开关,所述第一开关耦接在参考电压和所述esd保护电路的输入端之间,所述第二开关耦接在所述esd保护电路的输入端和输出端之间。

7.在一些可能的实现方式中,所述第一开关包括第一寄生二极管和第二寄生二极管,所述第一寄生二极管的负极与所述检波电路的电源耦接,所述第二寄生二极管的正极接地,所述第一寄生二极管的正极与所述第二寄生二极管的负极耦接。

8.在一些可能的实现方式中,所述第一开关包括第一p型晶体管和第一n型晶体管,所述第一p型晶体管和所述第一n型晶体管并联设置,所述第一寄生二极管寄生于所述第一p型晶体管,所述第一p型晶体管的衬底与所述检波电路的电源耦接,所述第二寄生二极管寄生于所述第一n型晶体管,所述第一n型晶体管的衬底接地。

9.在一些可能的实现方式中,所述第二开关包括第三寄生二极管和第四寄生二极管,所述第三寄生二极管的负极与所述检波电路的电源耦接,所述第四寄生二极管的正极接地,所述第三寄生二极管的正极与所述第四寄生二极管的负极耦接。

10.在一些可能的实现方式中,所述第二开关包括第二p型晶体管和第二n型晶体管,所述第二p型晶体管和所述第二n型晶体管并联设置,所述第三寄生二极管寄生于所述第二p型晶体管,所述第二p型晶体管的衬底与所述检波电路的电源耦接,所述第四寄生二极管

寄生于所述第二n型晶体管,所述第二n型晶体管的衬底接地。

11.在一些可能的实现方式中,还包括保护电阻,所述保护电阻耦接在所述esd保护电路的输入端和所述窗口选择开关之间。

12.在一些可能的实现方式中,还包括:

13.接地开关,所述接地开关的一端耦接所述esd保护电路的输入端,另一端接地,所述接地开关包括第五寄生二极管,所述第五寄生二极管的正极接地,所述第五寄生二极管的负极耦接所述esd保护电路的输入端。

14.在一些可能的实现方式中,所述接地开关包括第三n型晶体管,所述第五寄生二极管寄生于所述第三n型晶体管,所述第三n型晶体管的衬底接地。

15.第二方面,提供一种检波电路,用来检测接收电路的接收信号的幅度,所述检波电路包括

16.esd保护电路,包括窗口选择开关,所述窗口选择开关具有两个寄生二极管,其中一个所述寄生二极管的负极与所述检波电路的电源耦接,另一个所述寄生二极管的正极接地,所述一个寄生二极管的正极与所述另一个寄生二极管的负极耦接;

17.运算放大器,具有正端、负端与输出端;

18.积分电容,耦接于所述运算放大器的所述输出端与所述负端之间;

19.重置开关,与所述积分电容并联设置;

20.所述esd保护电路的窗口选择开关用于在所述检波电路的信号检测过程中切换采样模式和非采样模式。

21.在一些可能的实现方式中,所述窗口选择开关包括第一开关和第二开关,所述第一开关耦接在参考电压和所述接收电路的输出端之间、所述第二开关耦接在所述接收电路的输出端和所述运算放大器的负端之间。

22.在一些可能的实现方式中,所述第一开关包括第一寄生二极管和第二寄生二极管,所述第一寄生二极管的负极与所述检波电路的电源耦接,所述第二寄生二极管的正极接地,所述第一寄生二极管的正极与所述第二寄生二极管的负极耦接。

23.在一些可能的实现方式中,所述第一开关包括第一p型晶体管和第一n型晶体管,所述第一p型晶体管和所述第一n型晶体管并联设置,所述第一寄生二极管寄生于所述第一p型晶体管,所述第一p型晶体管的衬底与所述检波电路的电源耦接,所述第二寄生二极管寄生于所述第一n型晶体管,所述第一n型晶体管的衬底接地。

24.在一些可能的实现方式中,所述第二开关包括第三寄生二极管和第四寄生二极管,所述第三寄生二极管的负极与所述检波电路的电源耦接,所述第四寄生二极管的正极接地,所述第三寄生二极管的正极与所述第四寄生二极管的负极耦接。

25.在一些可能的实现方式中,所述第二开关包括第二p型晶体管和第二n型晶体管,所述第二p型晶体管和所述第二n型晶体管并联设置,所述第三寄生二极管寄生于所述第二p型晶体管,所述第二p型晶体管的衬底与所述检波电路的电源耦接,所述第四寄生二极管寄生于所述第二n型晶体管,所述第二n型晶体管的衬底接地。

26.在一些可能的实现方式中,还包括保护电阻,所述保护电阻耦接在所述esd保护电路的输入端和所述窗口选择开关之间。

27.在一些可能的实现方式中,还包括:

28.所述esd保护电路还包括接地开关,所述接地开关的一端耦接所述esd保护电路的输入端,另一端接地,所述接地开关包括第五寄生二极管,所述第五寄生二极管的正极接地,所述第五寄生二极管的负极耦接所述esd保护电路的输入端;

29.其中:

30.在重置阶段,所述重置开关导通及所述第二开关不导通,所述运算放大器的所述输出端输出参考电压;

31.在接收阶段,所述接地开关导通,所述重置开关、所述第一开关且所述第二开关均不导通,所述接收电路接收所述输入信号后产生所述接收信号。

32.在所述一般阶段,所述重置开关不导通,以及所述接收信号包含周期为t的多个波,所述检波电路在对应所述多个波中的第一特定波的周期t中,有t*r的时间被设置为所述采样模式,以及有t*(1-r)的时间被设置为所述非采样模式,其中r大于0且小于1;以及所述检波电路在对应所述多个波中的第二特定波的周期t中,有t*r的时间被设置为所述采样模式,以及有t*(1-r)的时间被设置为所述非采样模式,其中:

33.在所述采样模式,所述第一开关不导通且所述第二开关导通,使所述接收信号在所述采样模式期间的幅度改变依特定比例反应且累加在所述运算放大器的所述输出端;以及

34.在所述非采样模式,所述第一开关导通且所述第二开关不导通,使所述接收电路产生的所述接收信号在所述非采样模式的幅度改变不反应且不累加在所述运算放大器的所述输出端,使所述运算放大器的所述输出端的电压在所述非采样模式维持不变。

35.在一些可能的实现方式中,所述接地开关包括第三n型晶体管,所述第五寄生二极管寄生于所述第三n型晶体管,所述第三n型晶体管的衬底接地。

36.第三方面,提供了一种相关电子装置,包括上述第二方面或其各实现方式所述的检波器。

37.与现有技术相比,本技术实施例的有益效果在于:本技术实施例提供的esd保护电路能够通过开关自身寄生的二极管来实现静电电荷的泄放,能够防止电子器件被击穿,并且无需额外加入二极管、ggnmos或者gdpmos等器件来作为esd保护电路,不会引入较大的寄生电容,不会分走信号量,从而保证检波电路检测结果的准确性。

附图说明

38.图1a是本技术的esd保护电路的第一实施例的示意图;

39.图1b是图1的esd保护电路的等效电路的示意图;

40.图2a是p型晶体管的剖面示意图;

41.图2b是n型晶体管的剖面示意图;

42.图3a是本技术的esd保护电路的第二实施例的示意图;

43.图3b是图3a的esd保护电路的等效电路的示意图;

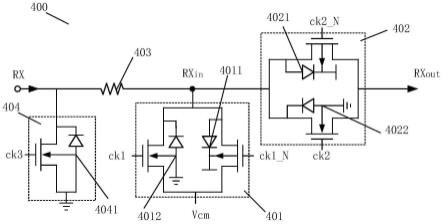

44.图4a是本技术的esd保护电路的第三实施例的示意图;

45.图4b是图4a的esd保护电路的等效电路的示意图;

46.图5a是本技术的esd保护电路的第四实施例的示意图;

47.图5b是图5a的esd保护电路的等效电路的示意图;

48.图6是包括图5a的esd保护电路的检波电路的示意图;

49.图7是图6的检波电路操作的时序图。

具体实施方式

50.下面将结合附图,对本技术中的技术方案进行描述。

51.本技术实施例提供的esd保护电路,是检波电路的一部分,其作用是为检波电路提供静电保护。该esd保护电路包括窗口选择开关,与普通的开关不同,本技术实施例的窗口选择开关具有正电荷泄放寄生二极管和负电荷泄放寄生二极管,其中,正电荷泄放寄生二极管的负极与检波电路的电源耦接,负电荷泄放寄生二极管的正极接地,正电荷泄放寄生二极管的正极与负电荷泄放寄生二极管的负极耦接。

52.当esd保护电路的输入端的电势升高为正值,并达到一定程度(大于检波电路电源的电势)时,由于正电荷泄放寄生二极管的负极与检波电路的电源耦接,该寄生二极管会导通,正电荷会从该寄生二极管的正极流向负极,并最终流向检波电路的电源,从而将正电荷泄放掉。

53.当esd保护电路的输入端的电势迅速降低,积累的负电荷不能及时泄放时,由于负电荷泄放寄生二极管的正极接地,该寄生二极管会导通,负电荷从该寄生二极管的负极流向正极,并最终流向大地,从而将负电荷泄放掉。

54.综上,输入端输入的正/负电荷会通过上述两个寄生二极管泄放掉,避免相关电子器件被击穿,与现有技术需要额外加入二极管、ggnmos或者gdpmos等器件来作为esd保护电路相比,本技术实施例的esd保护电路利用开关自身寄生的二极管来作为静电泄放通路,避免产生较大的寄生电容,不会分走一部分信号量,也就不会对传感器的性能产生影响,从而保证检波电路检测结果的准确性。此外,由于寄生电容的存在,传感器信号会流经该寄生电容,会影响传感器信号的传输速度,而本技术实施例的esd保护电路不存在寄生电容,则不会对传感器信号的传输速度产生影响。

55.以下对本技术的多个实施例进行论述。

56.参见图1a和图1b,图1a是本技术的esd保护电路100的第一实施例的示意图,图1b是图1a的esd保护电路100的等效电路的示意图。esd保护电路100作为检波电路的一部分,其作用是为检波电路提供静电保护。esd保护电路100包括第一开关101、第二开关102和保护电阻103,第一开关101和第二开关102构成窗口选择开关,第一开关101耦接在参考电压vcm和esd保护电路100的输入端r

x

之间,第二开关102耦接在esd保护电路100的输入端rx和输出端rx

out

之间,保护电阻103与第一开关101、第二开关102耦接,如图1a所示,第一开关101、第二开关102的耦接节点定义为rx

in

,保护电阻103耦接在esd保护电路100的输入端rx和节点rx

in

之间。其中,第一开关101受第一信号ck1、ck1_n控制,第一信号ck1、ck1_n是互补使能信号,可以同步控制第一开关101的导通与否,第二开关102受第二信号ck2控制。

57.进一步地,第一开关101为互补开关,具有两个寄生二极管,而第二开关102为普通开关,不具有寄生二极管。具体地,如图1a和图1b所示,第一开关101包括第一寄生二极管1011和第二寄生二极管1012,其中,第一寄生二极管1011为正电荷泄放寄生二极管,第二寄生二极管1012为负电荷泄放寄生二极管,第一寄生二极管1011的负极与检波电路的电源耦接,第二寄生二极管1012的正极接地,第一寄生二极管1011的正极与第二寄生二极管1012

的负极耦接。

58.参见图1a和图1b,当esd保护电路100的输入端rx的电势升高为正值,并达到一定程度(大于检波电路电源的电势)时,由于第一寄生二极管1011的负极与检波电路的电源耦接,第一寄生二极管1011会导通,正电荷会经由保护电阻103,从第一寄生二极管1011的正极流向负极,并最终流向检波电路的电源,从而将r

x

节点的正电荷泄放掉。由于保护电阻103的存在,正电荷在流过保护电阻103时,保护电阻103两端会存在较大的电压差,使得节点rx

in

的电压不会被迅速拉高,故节点rx

in

后的电子器件不会承担较大的电压,避免被击穿。

59.此外,当esd保护电路100的输入端rx的电势迅速降低,积累的负电荷不能及时泄放时,由于第二寄生二极管1012的正极接地,第二寄生二极管1012会导通,负电荷会经由保护电阻103,从第二寄生二极管1012的负极流向正极,并最终流向大地,从而将rx节点的负电荷泄放掉。由于保护电阻103的存在,负电荷在流过保护电阻103时,保护电阻103两端会存在较大的电压差,使得节点rx

in

的电压不会被迅速拉低,故节点rx

in

后的电子器件不会承担较大的电压,避免被击穿。

60.综上,输入端rx输入的正/负电荷会通过第一开关101的第一寄生二极管1011和第二寄生二极管1012泄放掉,避免相关电子器件被击穿,与现有技术需要额外加入二极管、ggnmos或者gdpmos等器件来作为esd保护电路相比,本技术实施例的esd保护电路利用开关自身寄生的二极管来作为静电泄放通路,避免产生较大的寄生电容,不会分走一部分信号量,也就不会对传感器的性能产生影响。此外,由于寄生电容的存在,传感器信号会流经该寄生电容,会影响传感器信号的传输速度,而本技术实施例的esd保护电路不存在寄生电容,则不会对传感器信号的传输速度产生影响。

61.如图1a所示,保护电阻103耦接在esd保护电路100的输入端rx和节点rx

in

之间。需要说明的是,在根据本技术的其他实施例中,保护电阻103可以串联在第一开关101所在的通路上,也就是耦接在节点rx

in

和第一开关之间。保护电阻103也可以串联在第二开关102所在的通路上,也就是耦接在节点r

x_in

和第二开关102之间。保护电阻103的设置方式根据具体应用情况而定。

62.在根据本技术的一个实施例中,第一开关101为互补开关,其包括第一p型晶体管111和第一n型晶体管112,第一p型晶体管111和第一n型晶体管112并联设置,第一p型晶体管111和第一n型晶体管112均为场效应mos管,第一寄生二极管1011寄生于第一p型晶体管111,第一p型晶体管111的衬底与检波电路的电源耦接,第二寄生二极管1012寄生于第一n型晶体管112,第一n型晶体管112的衬底接地。

63.参见图2a和图2b,现在介绍第一p型晶体管111和第一n型晶体管112的工作原理。

64.参见图2a,图2a是第一p型晶体管111的剖面示意图。p型晶体管111是pnp型场效应管,p型晶体管111包括源极1111、漏极1112、栅极1113和衬底1114,源极1111和漏极1112接到p型半导体上,衬底1114接到n型半导体上,栅极1113的金属栅极与n型半导体沟通之间设置有二氧化硅绝缘层。当负电压加在栅极1113上时,由于电场的作用,此时p型半导体的源极1111和漏极1112的正电子被吸引出来而涌向栅极1113,但由于氧化膜的阻挡,使得正电子聚集在两个p沟道之间的n型半导体中,从而形成电流,使源极1111和漏极1112之间导通。可以想象的是,两个p型半导体之间为一条沟,栅极电压的建立相当于为它们之间搭了一座

桥梁,该桥的大小由栅压的大小决定,因此可以通过控制栅极1113的输入电压来控制第一p型晶体管111的输出电流。

65.为了避免阈值电压的偏移,源极1111通常会与衬底1114连接在一起,因此源极1111和衬底1114之间不会形成寄生二极管,而在漏极1112和衬底1114会形成pn结,也就是会形成第一寄生二极管1011,漏极1112为第一寄生二极管1011的正极,衬底1114为第一寄生二极管1011的负极。

66.在根据本技术的实施例中,第一寄生二极管1011的衬底1114与检波电路的电源耦接,正常情况下,由于第一寄生二极管1011的方向性,检波电路的电源的电流无法从衬底1114流入漏极1111,而当esd保护电路100的输入端rx的电势升高为正值,并达到一定程度(大于检波电路电源的电势)时,由于衬底1114与检波电路的电源耦接,第一寄生二极管1011会导通,正电荷会经由保护电阻103,从第一寄生二极管1011的正极流向负极,并最终流向检波电路的电源,从而将rx节点的正电荷泄放掉。由于保护电阻103的存在,正电荷在流过保护电阻103时,保护电阻103两端会存在较大的电压差,故节点rx

in

后的电子器件不会承担较大的电压,避免被击穿。

67.参见图2b,图2b是第一n型晶体管112的剖面示意图,第一n型晶体管112的工作原理与第一p型晶体管111的工作原理类似,在此不做赘述。第一n型晶体管112的输出电流可以通过控制栅极1123的输入电压来控制,源极1121和衬底1124之间亦不会形成寄生二极管,而在漏极1122和衬底1124会形成pn结,也就是会形成第二寄生二极管1012,漏极1122为第二寄生二极管1012的负极,衬底1124为第二寄生二极管1012的正极。

68.在根据本技术的实施例中,第一n型晶体管112的衬底1124接地,由于第二寄生二极管1012的方向性,当esd保护电路100的输入端rx的电势迅速降低,积累的负电荷不能及时泄放时,由于第二寄生二极管1012的衬底1124接地,第二寄生二极管1011会导通,负电荷会经由保护电阻103,从第二寄生二极管1011的负极流向正极,并最终流向大地,从而将rx节点的负电荷泄放掉。由于保护电阻103的存在,负电荷在流过保护电阻103时,保护电阻103两端会存在较大的电压差,故节点rx

in

后的电子器件不会承担较大的电压,避免被击穿。

69.综上,输入端rx输入的正/负电荷会通过第一开关101的第一寄生二极管1011和第二寄生二极管1012泄放掉,避免相关电子器件被击穿,与现有技术需要额外加入二极管、ggnmos或者gdpmos(gate-to-drain等器件来作为esd保护电路相比,本技术实施例的esd保护电路利用开关自身寄生的二极管来作为静电泄放通路,避免产生较大的寄生电容,不会分走一部分信号量,也就不会对传感器的性能产生影响。此外,由于寄生电容的存在,传感器信号会流经该寄生电容,会影响传感器信号的传输速度,而本技术实施例的esd保护电路不存在寄生电容,则不会对传感器信号的传输速度产生影响。

70.参见图3a和图3b,图3a是本技术的esd保护电路200的第二实施例的示意图,图3b是图3a的esd保护电路200的等效电路的示意图,与图1a和图1b的esd保护电路100不同的是,本实施例的esd保护电路200的第一开关201为普通开关,而第二开关202具有寄生二极管,如图3a和图3b所示,第二开关202包括第三寄生二极管2021和第四寄生二极管2022,其中,第三寄生二极管2021为正电荷泄放寄生二极管,第四寄生二极管2022为负电荷泄放寄生二极管,第三寄生二极管2021的负极与检波电路的电源耦接,第四寄生二极管2022的正极接地,第三寄生二极管2021的正极耦接第四寄生二极管2022的负极,第三寄生二极管

2021和第四寄生二极管2022的结构和工作原理参照上文,在此不做赘述。

71.参见图4a和图4b,图4a是本技术的esd保护电路300的第三实施例的示意图,图4b是图4a的esd保护电路300的等效电路的示意图。与图1a的esd保护电路100和图2a的esd保护电路200不同的是,图4a的esd保护电路300的第一开关301和第二开关302均具有寄生二极管。

72.具体地,esd保护电路300的第一开关301包括第一寄生二极管3011和第二寄生二极管3012,其中,第一寄生二极管3011为正电荷泄放寄生二极管,第二寄生二极管3012为负电荷泄放寄生二极管。如图4a和图4b所示,第一寄生二极管3011的负极与检波电路的电源耦接,第二寄生二极管3012的正极接地,第一寄生二极管3011的正极耦接第二寄生二极管3012的负极。esd保护电路300的第二开关302包括第三寄生二极管3021和第四寄生二极管3022其中,第三寄生二极管3021为正电荷泄放寄生二极管,第二寄生二极管3022为负电荷泄放寄生二极管。如图4a和图4b所示,第三寄生二极管3021的负极与检波电路的电源耦接,第四寄生二极管3022的正极接地,第三寄生二极管3021的正极耦接第四寄生二极管3022的负极。

73.参见图4a和图4b,当esd保护电路300的输入端rx的电势升高为正值,并达到一定程度(大于检波电路电源的电势)时,由于第一寄生二极管3011和第三寄生二极管3021的负极与检波电路的电源耦接,第一寄生二极管3011和第三寄生二极管3021会导通,正电荷会经由保护电阻303,从第一寄生二极管3011和第三寄生二极管3021的正极流向负极,并最终流向检波电路的电源,从而将rx节点的正电荷泄放掉。由于保护电阻303的存在,正电荷在流过保护电阻303时,保护电阻303两端会存在较大的电压差,使得节点rx

in

的电压不会被迅速拉高,故节点rx

in

后的电子器件不会承担较大的电压,避免被击穿。

74.此外,当esd保护电路300的输入端rx的电势迅速降低,积累的负电荷不能及时泄放时,由于第二寄生二极管3012和第四寄生二极管3022的正极接地,第二寄生二极管3012和第四寄生二极管3022会导通,负电荷会经由保护电阻303,从第二寄生二极管3012和第四寄生二极管3022的负极流向正极,并最终流向大地,从而将rx节点的负电荷泄放掉。由于保护电阻303的存在,正电荷在流过保护电阻303时,保护电阻303两端会存在较大的电压差,使得节点rx

in

的电压不会被迅速拉低,故节点rx

in

后的电子器件不会承担较大的电压,避免被击穿。

75.如图4a和图4b所示,保护电阻303耦接在esd保护电路300的输入端rx和节点rx

in

之间。需要说明的是,在根据本技术的其他实施例中,保护电阻303可以串联在第一开关301所在的通路上,也就是耦接在节点rx

in

和第一开关301之间。保护电阻303也可以串联在第二开关302所在的通路上,也就是耦接在节点rx

in

和第二开关302之间。保护电阻303的设置方式根据具体应用情况而定。

76.在根据本技术的一个实施例中,第一开关301包括第一p型晶体管311和第一n型晶体管312,第一p型晶体管311和第一n型晶体管312并联设置,第一寄生二极管3011寄生于第一p型晶体管311,第一p型晶体管311的衬底与检波电路的电源耦接,第二寄生二极管3012寄生于第一n型晶体管312,第一n型晶体管312的衬底接地。第二开关302包括第二p型晶体管321和第二n型晶体管322,第二p型晶体管321和第二n型晶体管322并联设置,第三寄生二极管3021寄生于第二p型晶体管321,第二p型晶体管321的衬底与检波电路的电源耦接,第

四寄生二极管3022寄生于第二n型晶体管322,第二n型晶体管322的衬底接地。

77.第一p型晶体管311、第一n型晶体管312、第二p型晶体管321和第二n型晶体管322的工作原理参照上文所述,在此不做赘述。

78.参见图5a和图5b,图5a是本技术的esd保护电路400的第四实施例的示意图,图5b是图5a的esd保护电路400的等效电路的示意图。与图4a的esd保护电路400不同的是,图5a的esd保护电路400还包括接地开关404。接地开关404的一端耦接esd保护电路400的输入端rx,另一端接地。

79.esd保护电路400的第一开关401包括第一寄生二极管4011和第二寄生二极管4012,其中,第一寄生二极管4011为正电荷泄放寄生二极管,第二寄生二极管4012为负电荷泄放寄生二极管。如图5a和图5b所示,第一寄生二极管4011的负极与检波电路的电源耦接,第二寄生二极管4012的正极接地,第一寄生二极管4011的正极和第二寄生二极管4012的负极耦接。esd保护电路400的第二开关402包括第三寄生二极管4021和第四寄生二极管4022,其中,第三寄生二极管4021为正电荷泄放寄生二极管,第四寄生二极管4022为负电荷泄放寄生二极管。如图5a和图5b所示,第三寄生二极管4021的负极与检波电路的电源耦接,第四寄生二极管4022的正极接地,第三寄生二极管4021的正极和第四寄生二极管4022的负极耦接。esd保护电路400的接地开关404包括第五寄生二极管4041,该第五寄生二极管4041的正极接地。

80.一般地,接地开关404为大尺寸的n型晶体管,因而能够更好地实现接地效果,并且能够充当静电泄放通道。

81.参见图5a和图5b,接地开关404的第五寄生二极管4041构成初级esd保护电路,第一开关401的第一寄生二极管4011和第二寄生二极管4012、第二开关402的第三寄生二极管4021和第四寄生二极管4022构成次级esd保护电路。通常esd保护电路的输入端rx裸露在芯片外,容易积累电荷,当esd保护电路400的输入端rx积累的正电荷达到一定程度,电势升高为正值,并达到一定程度时,接地开关404的第五寄生二极管4041会反向导通,正电荷会通过第五寄生二极管4041泄放掉到大地。当输入端rx的电压迅速升高,超过检波电路的电源电压,并且第五寄生二极管4041无法及时泄放,由于第一寄生二极管4011和第三寄生二极管4021的负极与检波电路的电源耦接,第一寄生二极管4011和第三寄生二极管4021会导通,正电荷会经由保护电阻403,从第一寄生二极管4011和第三寄生二极管4021的正极流向负极,并最终流向检波电路的电源,从而将rx节点的正电荷泄放掉。由于保护电阻403的存在,正电荷在流过保护电阻403时,保护电阻403两端会存在较大的电压差,使得节点rx

in

的电压不会被迅速拉高,故节点rx

in

后的电子器件不会承担较大的电压,避免被击穿。

82.此外,当esd保护电路400的输入端rx积累负电荷到一定程度,输入端rx的电势会变为负值,并达到一定程度时,接地开关404的第五寄生二极管4041会导通,负电荷会通过第五寄生二极管4041泄放掉到大地。当输入端rx的电压迅速降低,并且第五寄生二极管4041无法及时泄放,由于第二寄生二极管4012和第四寄生二极管4022的正极接地,第二寄生二极管4012和第四寄生二极管4022会导通,负电荷会经由保护电阻403,从第二寄生二极管4012和第四寄生二极管4022的负极流向正极,并最终流向检大地,从而将rx节点的负电荷泄放掉。由于保护电阻403的存在,负电荷在流过保护电阻403时,保护电阻403两端会存在较大的电压差,使得节点rx

in

的电压不会被迅速拉低,故节点rx

in

后的电子器件不会承担

较大的电压,避免被击穿。

83.综上,输入端rx累积的正/负电荷会通过第一开关401、第二开关402和/或接地开关404的寄生二极管泄放掉,避免相关电子器件被击穿,与现有技术需要额外加入二极管、ggnmos或者gdpmos等器件来作为esd保护电路相比,本技术实施例的esd保护电路利用开关自身寄生的二极管来作为静电泄放通路,避免产生较大的寄生电容,不会影响传感器信号的传输速度或者分走一部分信号量,也就不会对传感器的性能产生影响。

84.进一步地,第一寄生二极管4011、第三寄生二极管4021寄生在p型晶体管上,第二寄生二极管4012、第四寄生二极管4022和第五寄生二极管4041寄生在n型晶体管上。具体工作原理,可以参考上文所述,在此不做赘述,

85.如图5a和图5b所示,保护电阻403耦接在esd保护电路100的输入端rx和节点rx

in

之间。如上文所述,保护电阻403的设置方式可以根据具体应用情况而定。

86.参见图6,图6是包括图5a和图5b的esd保护电路的检波电路60的示意图。检波电路60用来判断接收电路61的在节点rx

ini

上的接收信号vs的幅度。

87.如图6所示,检波电路60包括esd保护电路62、运算放大器601、电容单元602和重置开关603,运算放大器601、电容单元602和重置开关603构成积分电路。

88.具体地,esd保护电路62包括第一开关621、第二开关622和接地开关623和保护电阻624,第一开关621、第二开关622构成窗口选择开关,第一开关621、第二开关622和接地开关623均与保护电阻624耦接。运算放大器601具有正端(+)、负端(-)与输出端。电容单元602耦接于运算放大器601的输出端与负端(-)之间。重置开关603与电容单元602并联设置。第一开关621耦接于参考电压vcm及节点rx

in

之间,此处的节点rx

in

是窗口选择开关的输入端。如图6所示,参考电压vcm由数模转换器dac和运算放大器opa1提供。第二开关622耦接于节点rx

in

与运算放大器106的负端(-)之间,接地开关623耦接于输入节点rx与地之间。运算放大器601的正端(+)耦接于参考电压vcm。其中重置开关603受信号rst控制,第一开关621受信号ck1控制,第二开关621受信号ck2控制,接地开关621受信号ck3控制。

89.在本实施例中,如上文所述,第一开关621、第二开关622为互补开关,第一开关621、第二开关622分别有两个寄生二极管,第一开关621和第二开关622均由p型晶体管和n型晶体管并联设置而成,并且p型晶体管的衬底都接检波电路60的电源,而n型晶体管的衬底均接地。重置开关603和接地开关623可以使用n型晶体管来实现,并且接地开关624的衬底接地。

90.如上所述,输入端rx累积的正/负电荷会通过第一开关621、第二开关622和/或接地开关623的寄生二极管泄放掉,避免相关电子器件被击穿,与现有技术需要额外加入二极管、ggnmos或者gdpmos等器件来作为esd保护电路相比,本技术实施例的检波电路60通过esd保护电路的开关自身寄生的二极管来作为静电泄放通路,避免产生较大的寄生电容,不会影响传感器信号的传输速度或者分走一部分信号量,也就不会对传感器的性能产生影响。

91.接收电路61等效地包含接收电阻611及接收电容612。接收电阻611与接收电容612耦接。接收信号vs流经接收电阻611后,由接收电容612接收。其中电容单元602的电容值为ci,接收电容612的电容值为cs。

92.需要说明的是,图6示出的检波电路61包括的是如图5a和图5b所示的esd保护电

路,在本技术的检波电路的其他实施例中,检波电路61可以包括如图1a和图1b所示的第一实施例、图3a和图3b所示的第二实施例或图4a和图4b所示的第三实施例的esd保护电路,以上各esd保护电路的静电释放方式如上文所述,在此不做赘述。

93.参见图7,图7为图6的检波电路操作上的一个实施例的时序图。接收信号vs包含周期为t(例如时间点t3至时间点t5)的正弦波的多个波。本技术的检波电路60可用来对接收信号vs的幅度进行采样,由于接收信号vs的幅度可能很小,因此为了增加检波电路60的灵敏度,检波电路60会针对多个周期的接收信号vs以积分的方式进行幅度采样,并将多个周期的采样结果累积起来。本技术的检波电路60不仅适用于正弦波样态的情况。在某些实施例中,还可以适用于三角波或梯型波等样态。只要上述波的波谷升至波峰的上升沿的斜率小于90度,及波峰降至波谷的下降沿的斜率大于-90度即可。

94.在图7中,vs表示节点rx

ini

处的接收信号,rx表示rx节点处的信号,v

out

表示检波电路60的输出信号。

95.在时间点t1之前,检波电路60进入重置阶段。在所述重置阶段,信号rst为高电压电平使重置开关603导通,信号ck1为低电压电平使第一开关622不导通,信号ck2为低电压电平使第二开关623不导通,信号ck3为低电压电平使接地开关624不导通,由于运算放大器601形成负反馈,运算放大器601的输出端及负端(-)电压会被限制和正端(+)电压相同,即参考电压vcm。且电容单元602两端电压相同使其电容值被清零。此外,在所述重置阶段,信号ck1可以为高电压电平使第一开关622导通,以顺便对接收电路61的接收电容612进行重置。

96.在本技术的一个实施例中,检波电路60用于对超声波指纹识别芯片发出的超声波信号进行检测,超声波指纹识别芯片的压电材料的下极板需要接地或者接到固定电平,即esd保护电路62的输入端rx接地或者接到固定电平,此时,压电材料会发射超声波。当然,本技术提供的检波电路60不限于检测超声波指纹芯片发出的超声波信号。

97.如图7所示,在所接收的信号在时间点t1及时间点t2之间为接收阶段,信号ck3为高电压电平使接地开关623导通,重置开关603、第一开关621且第二开关622均不导通,esd保护电路62的输入端rx接地,超声波指纹识别芯片发出的超声波信号,检波电路60的收到该信号vs。

98.在时间点t2及时间点t7之间为一般阶段,重置开关603和接地开关623不导通。在图7所示的操作实施例中,时间点t3、时间点t5对齐接收信号vs的连续两个波谷;时间点t4及时间点t6对齐接收信号vs的连续两个波峰。时间点t3至时间点t5的时间长度等于接收信号vs的周期t。

99.具体来说,在所述一般阶段若要对接收信号vs进行幅度的采样,第一开关621和第二开关622需要依据接收信号vs的频率进行开关。在图7所示的操作实施例中,在时间点t3至时间点t4之间的时间以及时间点t5至时间点t6之间的时间,信号ck1为低电压电平使第一开关621不导通,信号ck2为高电压电平使第二开关622导通,使检波电路60进入采样模式。在一般阶段的其余时间,第一开关621导通且第二开关622不导通,使检波电路60进入非采样模式。因此,对时间点t3开始的连续两个周期来说,各周期中有一半的时间(t*0.5)检波电路60在所述采样模式,以及另一半的时间(t*0.5)检波电路60在所述非采样模式。

100.在图7中,虽然时间点t7的波谷的幅度略小于对应时间点t5的波谷的幅度,但是时

间点t6至时间点t7之间的时间处于非采样模式,不会对输出的电压产生影响。

101.如图7所示,在每次采样模式中,接收信号vs的电压改变量会依特定比例反应且累加在运算放大器601的输出端,并贡献δvout。以时间点t3至时间点t4之间的时间为例,若接收信号vs的幅度为va,接收信号vs由波谷升至波峰,即接收信号vs在时间点t3至时间点t4的电压改变量为2*va,则δvout=-2*va*cs/ci,使运算放大器601的输出端的电压vout由参考电压vcm往上累积。由于δvout和接收信号vs的幅度va正比,因此可以实现检波作用,并且每重复一次采样模式的过程,运算放大器601的输出端的电压vout都会增加δvout,可以重复针对k个周期进行k次采样模式,使输出电压,不断累积上升。此时,δvout通过如下公式(1)获得:

[0102][0103]

经过多次积分,以提高检波电路60的灵敏度。其中k为整数,图7中k为2仅为示意,本技术不限制k的范围,只要为大于0的整数即可。但为体现本技术的优势,k可以被提高,例如在100到1000的数量级范围。

[0104]

此外,还可以n个信号进行积分,并且对其中信号中的k个周期进行k次采样、积分,以进一步提高提高检波电路60的灵敏度。此时,δvout通过如下公式(2)获得:

[0105][0106]

其中k、n为整数,本技术不限制k、n的范围,只要为大于0的整数即可。

[0107]

在上述过程中,积分结果大小取决接收信号vs的信号量大小。若引入额外的esd保护电路,将会引入较大的寄生电容。由于积分电路有限的带宽,导致一部分信号量会被寄生电容消耗掉,造成积分结果产生偏差。本技术的检波电路60采用窗口选择开关621、622寄生的二极管作为esd泄放通道,从而在不引入额外泄放通路的基本上,既提供了静电释放的功能,又不牺牲传感器电路本身的性能。

[0108]

在每次非采样模式中,接收信号vs的电压改变量不会反应且不会累加在运算放大器601的输出端,使运算放大器601的输出端的电压vout在所述非采样模式维持不变。以时间点t4至时间点t5之间的时间为例,接收信号vs由波峰降至波谷,但因第一开关621导通且第二开关622不导通,因此接收信号vs的电压改变量-2*va不会影响运算放大器601的输出端的电压vout。因此不会抵销掉时间点t3至时间点t4收信号vs的电压改变量对电压vout累加的量。

[0109]

图7描述的时序图的采样模式是接收信号vs在波谷升至波峰的时间进行,在本技术的其他实施例中,采样模式也可以设置为在接收信号vs在波峰降至波谷的时间进行,或者设置为从接收信号vs的波峰之后一段时间才开始进行,并在波谷来到之前便结束,还可以设置为从接收信号vs的波谷之后一段时间才开始进行,并在波峰来到之前便结束,在此不作限定。

[0110]

本技术还提出一种包含检波电路60的电子装置。具体的,所述电子装置包括但不限于移动通信设备、超移动个人计算机设备、便携式娱乐设备和其他具有数据交互功能的电子设备。移动通信设备的特点是具备移动通信功能,并且以提供话音、数据通信为主要目标。这类终端包括:智能手机(例如iphone)、多媒体手机、功能性手机,以及低端手机等。超

移动个人计算机设备属于个人计算机的范畴,有计算和处理功能,一般也具备移动上网特性。这类终端包括:pda、mid和umpc设备等,例如ipad。便携式娱乐设备可以显示和播放多媒体内容。该类设备包括:音频、视频播放器(例如ipod),掌上游戏机,电子书,以及智能玩具和便携式车载导航设备。

[0111]

应理解,本技术实施例中的具体的例子只是为了帮助本领域技术人员更好地理解本技术实施例,而非限制本技术实施例的范围,本领域技术人员可以在上述实施例的基础上进行各种改进和变形,而这些改进或者变形均落在本技术的保护范围内。

[0112]

以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1