一种集成采样电阻的充电芯片的制作方法

1.本发明涉及集成电路,更具体地,涉及一种集成采样电阻的充电芯片。

背景技术:

2.目前,充电芯片(charge ic)在应用过程中,通常需要外接采样电阻,以确保充电芯片输出电流的稳定程度符合要求。在对充电芯片的实用过程中,工程师们通常会自行购买合适的高精度电阻作为采样电阻,并通过芯片管脚引出合适的信号与采样电阻进行连接。

3.现有技术中,在芯片外部使用外置的采样电阻,不仅会增加电路的成本,导致芯片使用不便的问题,还会因为外置的采样电阻的精确度不够、连接方式产生损耗等原因使得芯片输出信号的质量下降,精度降低。然而,现有技术也不存在能够将采样电阻内置在充电芯片中的技术方案,以及将采样电阻内置在充电芯片中并合理布局的技术方案。

4.因此,亟需一种新型的充电芯片,能够将采样电阻内置其中,并提高输出精度。

技术实现要素:

5.为解决现有技术中存在的不足,本发明的目的在于,提供一种集成采样电阻的充电芯片,能够将采样电阻与参考电阻临接摆放,从而抵消工艺偏差。

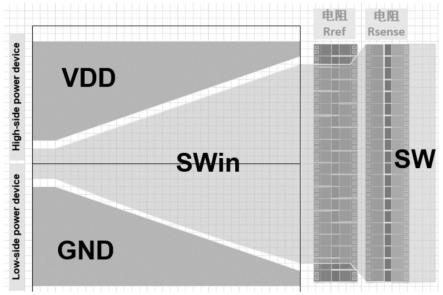

6.本发明采用如下的技术方案。一种集成采样电阻的充电芯片,包括高边驱动电路hsd、低边驱动电路lsd、开关电路sw、参考电阻r

ref

。充电芯片还包括采样电阻r

sense

,采样电阻r

sense

用于为芯片提供恒定的输出电流;充电芯片开关控制sw引脚区域的版图布置为:高边驱动电路hsd位于区域的左上方,低边驱动电路lsd位于区域的左下方与高边驱动电路hsd对称设置;开关电路sw位于区域的中部;参考电阻r

ref

位于开关电路sw、高边驱动电路hsd以及低边驱动电路lsd的右侧;采样电阻r

sense

与参考电阻r

ref

临接,且位于参考电阻r

ref

的右侧。

7.优选地,采样电阻r

sense

包括多个十欧姆量级的走线电阻或poly电阻,多个电阻首尾并联,且每个水平放置,整体纵向排列,每一电阻左右两侧各包括两个外部电极。

8.优选地,参考电阻r

ref

包括多个十欧姆量级的走线电阻或poly电阻,多个电阻由上至下依次串联,且每个水平放置,整体纵向排列,每一电阻左右两侧各包括两个外部电极。

9.优选地,参考电阻r

ref

与采样电阻r

sense

等宽等长、类型相同、数量相等;参考电阻r

ref

与采样电阻r

sense

并列平行放置,并设置于开关控制sw引脚内侧。

10.优选地,输入电压vdd引脚开窗位于区域的上方,地电位gnd引脚开窗位于区域的下方,开关控制sw引脚开窗位于区域的右侧,与并联电阻相邻,以便于连接并联电阻。

11.优选地,充电芯片开关控制sw引脚区域的版图布置中,从左到右,高边驱动电路hsd和低边驱动电路lsd所占面积逐渐减小,开关电路sw所占面积逐渐增加。

12.优选地,以参考电阻r

ref

与采样电阻r

sense

的间隔、参考电阻r

ref

与采样电阻r

sense

中每一电阻的间隔最小为原则实现版图布置。

13.优选地,充电芯片开关控制sw引脚的恒流输出电流为:

[0014][0015]

其中,r

ref

为芯片内部电路所连接的部分参考电阻的电阻值;r

sense

为开关控制sw引脚所连接的部分采样电阻的电阻值;v

ref

为芯片内部电路输出的参考电压;r

ccset

为片外恒流值设置电阻

[0016]

本发明的有益效果在于,与现有技术相比,本发明中一种集成采样电阻的充电芯片,能够将采样电阻集成于充电芯片的内部,并将采样电阻与参考电阻临接摆放,以抵消工艺偏差,从而使得充电芯片实现节约成本、便利应用和提高精度的目的。

附图说明

[0017]

图1为本发明中一种集成采样电阻的充电芯片的版图布置示意图。

具体实施方式

[0018]

下面结合附图对本技术作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本技术的保护范围。

[0019]

图1为本发明中一种集成采样电阻的充电芯片的版图布置示意图。如图1所示,一种集成采样电阻的充电芯片,包括高边驱动电路hsd、低边驱动电路lsd、开关电路sw、参考电阻r

ref

,其特征在于:充电芯片还包括采样电阻r

sense

,采样电阻r

sense

用于为芯片提供恒定的输出电流。

[0020]

充电芯片开关控制sw引脚区域的版图布置为:高边驱动电路hsd位于该区域的左上方,低边驱动电路lsd位于芯片基板的左下方与所述高边驱动电路hsd对称设置;开关电路sw位于区域的中部。

[0021]

在本发明芯片开关控制sw引脚区域的布局中,为了减小面积,提高集成度,并且使得电路布局更好地适应引脚开窗的布置,可以设置高边驱动电路hsd和低边驱动电路lsd分别置于芯片基板的两侧,并在芯片基板的中部位置放置开关电路sw。

[0022]

优选地,设置输入电压vdd引脚开窗位于区域的上方,地电位gnd引脚开窗位于区域的下方,开关控制sw引脚开窗位于区域的右侧,与并联电阻相邻,以便于连接所述并联电阻。本发明一实施例中,对应于充电芯片内部的电路设计,可以在开关电路sw引脚位置分别设置两个输入电压vdd引脚开窗,两个地电位gnd引脚开窗以及四个开关控制sw引脚开窗。

[0023]

另外,充电芯片的版图布置中,随着芯片从左到右,高边驱动电路hsd和低边驱动电路lsd所占面积逐渐减小,开关电路sw所占面积逐渐增加。

[0024]

优选地,参考电阻r

ref

位于开关电路sw、高边驱动电路hsd以及低边驱动电路lsd的右侧;采样电阻r

sense

与参考电阻r

ref

临接,且位于参考电阻r

ref

的右侧。

[0025]

具体的,采样电阻r

sense

包括多个十欧姆量级的走线电阻或poly电阻,且由上述多个电阻并联形成毫欧姆量级的采样电阻r

sense

。上述多个电阻每个水平放置,整体纵向排列,每一电阻左右两侧各包括两个外部电极。同样的,参考电阻r

ref

包括多个十欧姆量级的走线电阻或poly电阻且上述多个电阻由上至下依次串联形成百欧姆量级的参考电阻r

ref

,每一电阻左右两侧各包括两个外部电极。

[0026]

优选地,参考电阻r

ref

与所述采样电阻r

sense

等宽等长、类型相同、数量相等。由于参考电阻r

ref

与采样电阻r

sense

的外在形态、尺寸、数量相同或类似,并且并列平行摆放,因此在根据版图设计制造相应的掩模板并执行光刻、显影、清洗等一系列的工艺过程中最大程度上抵消了工艺偏差,使得生产出的芯片成品中参考电阻与采样电阻受到的芯片制造影响和环境影响所致误差相同,从而保证芯片的输出信号效果最优。同时,参考电阻r

ref

与采样电阻r

sense

并列平行放置,并设置于开关控制sw引脚内侧。

[0027]

另外,以参考电阻r

ref

与采样电阻r

sense

的间隔、参考电阻r

ref

与采样电阻r

sense

中每一电阻的间隔最小为原则实现版图布置。

[0028]

优选地,充电芯片开关控制sw引脚的恒流输出电流为:

[0029][0030]

其中,r

ref

为芯片内部电路所连接的部分参考电阻的电阻值;r

sense

为开关控制sw引脚所连接的部分采样电阻的电阻值;v

re

f为芯片内部电路输出的参考电压;r

ccset

为片外恒流值设置电阻。由此可知,充电芯片开关控制sw引脚的恒流输出电流与参考电阻的阻值成正比,与采样电阻成反比。

[0031]

本发明的有益效果在于,与现有技术相比,本发明中一种集成采样电阻的充电芯片,能够将采样电阻集成于充电芯片的内部,并将采样电阻与参考电阻临接摆放,以抵消工艺偏差,从而使得充电芯片实现节约成本、便利应用和提高精度的目的。

[0032]

本发明申请人结合说明书附图对本发明的实施示例做了详细的说明与描述,但是本领域技术人员应该理解,以上实施示例仅为本发明的优选实施方案,详尽的说明只是为了帮助读者更好地理解本发明精神,而并非对本发明保护范围的限制,相反,任何基于本发明的发明精神所作的任何改进或修饰都应当落在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1