电感器阵列和支撑件的制作方法

电感器阵列和支撑件

背景技术:

1.电感器有许多应用,尤其是在模拟电路、信号处理和半导体器件中。电感器是一种无源双端电组件,当电流流过它时,其在磁场中存储能量。电感器通常由缠绕成线圈的绝缘导线组成。应用的范围可以从在电源中使用与滤波电容器一起工作以从直流输出中去除纹波的大电感器,到由安装在电缆周围的用于防止射频干扰沿导线传输的铁氧体磁珠或环体制成的小电感器。

2.对于半导体器件来说,电感器是用在开关电压调节器(vr)系统中的主要组件之一。当半导体“导通”时,电感器中的电流斜坡上升并且能量被存储,而当其“断开”时,所存储的能量被释放到负载中。电感器向电路供应能量以在“断开”开关期间保持电流流动,并且实现其中输出电压高于输入电压的拓扑。在开关周期期间电感器中的电流变化量被称为纹波电流,并且vr系统对传入脉冲电压的纹波进行滤波。

3.电感器的存在可能影响印刷电路板(pcb)迹线的电特性,这是随着电子组件速度持续增加的重要考虑因素。作为一种设计的“经验法则”,由于归因于电感器的磁场(h场)的显著噪声耦合可能会导致信号质量降级(例如,可能会减小信号传输带宽的增加的信号抖动),所以通常禁止将信号路由/迹线直接放置在pcb中的电感器组件下方。当尝试积极地减小电路板尺寸时,信号路由的设置的这种限制可能会受到重大挑战。

附图说明

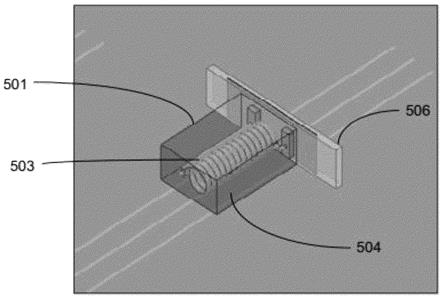

4.在附图中,相同的附图标记遍及不同的视图通常表示相同的部件。附图不一定按比例绘制,而是重点通常放在说明本公开的原理上。为了清楚起见,各种特征或要素的尺寸可以任意地扩大或缩小。在以下描述中,参考以下附图来描述本公开的各个方面,其中:图1示出电感器的磁场的说明性表示;图2示出具有半导体器件和电感器的多层电路板的说明性表示;图2a示出根据图2所示的器件的电感器的磁场的说明性表示;图3示出根据本公开的一个方面的具有电感器的器件的示例性截面图;图4示出根据本公开的另一方面的电感器和支撑板的示例性透视图;图5示出根据本公开的又一方面的电感器和支撑板的示例性透视图;图5a示出根据图5所示的方面的电感器和支撑板的截面图;图6示出常规电感器与根据本公开的一个方面的水平电感器的示例性占用面积的并排比较;图7示出根据本公开的又一方面的电感器阵列和支撑板的示例性透视图;图7a示出根据图7所示的方面的电感器阵列和支撑板的截面图;图8示出根据本公开的另一方面的示例性水平电感器;图9示出来自常规垂直电感器和根据本公开的一个方面的水平电感器的噪声耦合之间的比较;图10示出根据本公开的又一方面的来自水平电感器的感应电压和电流的示例性

表示;图11示出根据本公开的一个方面的示例性计算设备;以及图12示出根据本公开的一个方面的示例性方法的简化流程图。

具体实施方式

5.以下详细描述参考附图,附图以图示的方式示出了可实践本发明的特定细节和方面。这些方面被足够详细地描述以使本领域技术人员能够实践本公开。针对设备提供了各种方面,并且针对方法提供了各种方面。应当理解,设备的基本特性也适用于方法,反之亦然。可以利用其他方面,并且可以进行结构和逻辑上的改变,而不脱离本公开的范围。各个方面不一定是相互排斥的,因为一些方面可以与一个或多个其他方面组合以形成新的方面。

6.通常,电感器由导电材料(通常为绝缘铜线)的线圈组成,其缠绕在塑料或介电材料(以产生空心电感器)或铁磁材料的“芯”周围,其被称为“铁芯”电感器。铁磁芯的高磁导率增大了磁场,并将其局限成靠近电感器,从而增大了电感。电感器通常可以具有围绕线圈线的介电材料的壳体以提供机械支撑,其包括填充形成芯的线圈线的中心区的介电材料。

7.在图1所示的表示中,线圈电感器101具有穿过由导线102的缠绕形成的中心空间或芯的磁场103。磁场103由通过导线的电流所产生,并且当线圈线体水平放置时从北磁极(n)定向地移动到南磁极(s)。

8.如图2所示,典型的器件200可以具有“垂直”电感器201和位于具有若干层的印刷电路板(pcb)202上的半导体器件203(例如场效应晶体管)。对于典型的布局设计,由于磁场(也称为h场)引起的显著噪声耦合,pcb上的电感器组件的正下方(即,“禁区”)将不设置信号路由/迹线。

9.如图2a中提供的表示中所示,电感器的h场的可能效应可以达到远至pcb的第3层。信号路由可能需要被放置在第4层向前,并且可能仍然被限制于非关键或低速信号(<1gbps)。“关键”信号路由(例如,对于时钟信号和/或具有≥10gbps的数据速率的高速信号)可能需要从第7层开始向前放置,这可能会增加pcb和/或母板层数和/或需要额外的pcb基板面以避免电感器的h场的影响。

10.根据本公开,使其线圈线体水平取向的电感器可以针对高速多gbps信号(>20gbps)提供改进的信号完整性和性能,例如针对串行器/解串器(serdes)和外围组件互连高速(pcie)信号。其可允许使用较短的垂直过渡(例如,微通孔),且通过邻近于pcb表面(即,在开关vr模块电感器附近的相同层/区域)路由这些信号而使信号反射或串扰噪声耦合最小化。另外,通过消除相关联的垂直电感器x-y占用面积以及对于邻近垂直电感器组件的pcb布线禁用区的需要,使用当前公开的水平电感器和水平电感器阵列可以实现平台小型化。

11.通过参考以下描述和附图,本文所公开的各方面的这些和其他前述优点和特征将是显而易见的。此外,应当理解,本文描述的各个方面的特征不是相互排斥的,并且可以以各种组合和排列存在。

[0012] 在本公开的一个方面中,如图3所示,示例性器件300可以具有位于pcb 302上的“水平”电感器301。电感器301具有中心轴,其被示为a-a'虚线,其被水平地取向或平行于

pcb 302的表面,并且创建类似于图1所示的h场。在该配置中,水平电感器可以生成在方向上跟随信号路由线的磁场线。在此方面,水平电感器301可具有线圈线体303、壳体304和可耦合到支撑板306的两个连接构件305(仅示出一个)。同样在该方面,根据本公开,可以将多条信号路由线或迹线312(关键的和非关键的)放置在从pcb 302的表面起的第二层中,并且放置在下面的层中(即,第3层、第4层、第5层等)。在一方面,支撑板306可被定位成垂直于pcb 302的表面。连接构件305可以连接到线圈线303的端头。在一方面,壳体304可由各种材料制成,包括铁氧体材料、介电层和/或环氧聚合物树脂复合物。

[0013] 同样如图3所示,支撑板306可以具有使用焊膏308或其他导电粘合剂耦合到pcb 302上的接触焊盘309的导电层307。在另一方面,作为一个示例,支撑板306可以由刚性材料制成,诸如具有增强玻璃纤维的环氧树脂,并且导电层307可以由铜制成。在一方面,导电层307可包括其间具有交错介电层的两个或更多个导电层。由于减少的噪声耦合,水平电感器301的使用可以允许信号线被放置在水平电感器301之下的pcb 302的表面起的第二层中。应当理解,线圈线体303是根据本公开的水平电感器的示例,并且也可以使用产生类似h场的其他电感器体。

[0014]

具有根据需要(即,“混合和匹配”)来使用常规垂直电感器和本发明水平电感器两者的器件是在本发明范围内的。在这一方面,垂直电感器可以被定位成远离被放置在pcb表面起的第二层中的信号线。

[0015]

在图4中,示出了根据本公开的另一方面的电感器401和支撑板406的示例性透视图。在这个方面,电感器401可以具有中心轴,其被示为a-a'虚线,其被水平地配置或者平行于信号/迹线412,该信号/迹线可以从pcb(未示出)的表面之下的第二层开始放置。此外,可能需要支撑件以将电感器401和支撑板406可附接地固定到pcb;例如,在一个方面,可以如图4所示提供支架支撑件410a和410b。在一个方面,支架支撑件410a和410b可以通过表面安装工艺附接到pcb。在一方面,支架支撑件410a和410b可延伸以向平行布置的两个或更多个支撑板(未示出)提供机械支撑。提供使用不同设计的这种支撑件是在本公开范围内的;例如,图5a中所示的壳体支撑件514。

[0016]

图5示出了根据本公开的又一方面的水平电感器501的示例性透视图,并且图5a示出了其截面图。在这个方面,电感器501可以具有延伸的或延长的线圈线503和壳体504,以提供所需的电感容量并符合给定的高度限制。

[0017] 典型的垂直电感器可具有大约7

×6×

3 mm(即,x长度、y宽度、z高度)的尺寸和大约0.1μh的电感值。如果存在z高度限制,则图3所示的配置可能是不合适的。

[0018]

因此,为了实现类似的电感值,可能需要增加线圈线503的匝数,同时可以减小铁氧体磁芯面积,如图5所示。

[0019] 如图5a所示,支撑板506的z高度可以减小到例如3 mm或更小,以便等于或低于常规的垂直电感器。并且,x长度又可以根据需要增加,从而水平电感器可以用在具有z高度约束的计算设备中。在一方面,水平电感器可具有在2 mm到6 mm范围内的x长度,其可取决于性能和设计考虑而进一步增加。在另一方面,壳体504的高度可以与支撑板506的高度对齐。在另一方面,水平电感器501可具有壳体支撑件514以进一步固定水平电感器501。在又一方面,壳体支撑件514可以包括粘合剂膜层、金属框架或聚合物间隔件。

[0020] 图6示出根据本公开的一方面的水平电感器600a的阵列的示例性pcb占用面积与

常规垂直电感器600b的阵列的并排比较。在此方面,水平电感器600a的阵列的pcb占用面积可包括附接到pcb 602上的支撑板606的三个延伸的线圈线603,且常规垂直电感器600b的阵列的pcb占用面积可包括附接到pcb 602的四个垂直电感器620。根据本公开,水平电感器600a的阵列的pcb占用面积可以小于常规垂直电感器600b的阵列的pcb占用面积的一半。

[0021] 此外,水平电感器600a阵列的pcb占用面积可允许紧凑的pcb布局,其中,高密度信号线612可放置在水平电感器正下的pcb 602的第二层中。在另一方面,用于三个水平电感器阵列(在支撑板606下方)的pcb接触焊盘占用面积也可以小于用于四个垂直电感器阵列600b的pcb接触焊盘占用面积(等于连接构件605a和605b的占用面积)的一半。

[0022] 根据本公开的又一方面,图7示出了水平电感器阵列701和“双面”支撑板706的示例性透视图,并且图7a示出了其截面图。水平电感器阵列701可以具有耦合到双面支撑板706的延长的线圈线体703a、703b、703c、703d、703e和703f。在这个方面,延长的线圈线体703a、703b、703c、703d、703e和703f可以具有与图7中所示的相同的长度。同样在这个方面,双面支撑板706可以在pcb 702的表面上具有小的接触焊盘占用面积713。使用两个背靠背定位的单面支撑板代替双面支撑板也在本发明的范围内。

[0023] 在一些方面中,水平阵列701可具有不同配置(例如,其中,仅延长线圈线体703a、703c、703d和703f耦合到双面支撑板706,或仅延长线圈线体703a、703c和703e耦合到双面支撑板706)以及其他配置。改变在配置阵列中使用的水平电感器的延长线圈线体的长度以优化其性能也在本公开的范围内。在一方面,延长线圈线体703a、703b和703c可具有第一长度,例如为2至4 mm,并且703d、703e和703f可具有第二长度,第二长度可大于第一长度,例如为4至6 mm。在另一方面,阵列的配置可以具有并排的具有不同长度的水平电感器,例如长-短-长和/或短-长-短。在另一方面,水平电感器阵列701可以具有在延伸的线圈线(未示出)下方的支撑件,类似于图5a中所示的壳体支撑件514。

[0024]

图8示出了根据本公开的另一方面的示例性水平电感器801。水平电感器801可以位于pcb(未示出)上以产生定向地跟随信号路由线的中心磁场线,而不需要支撑板。在该方面,水平电感器801可以具有被支撑在端子连接构件805a和805b之间的线圈线体806。

[0025]

图9示出了来自常规垂直电感器与本公开的水平电感器的噪声耦合之间的比较。在该测试中,从距离相应电感器占用面积大约50密耳放置的迹线(即,微带信号通道)进行磁场噪声耦合测量。如图9所示,与常规的垂直线圈电感器所产生的感应电压相比,本发明的水平线圈电感器仅产生约20%的感应电压。

[0026] 图10示出了根据本公开的又一方面的来自pcb 1002上的水平电感器1001的感应电压和感应电流的示例性表示,其中,高密度信号线1012可以从水平电感器正下的pcb 1002的第二层开始放置。来自水平电感器的磁场与pcb中的信号路由线之间的相互作用可以在信号路由线上感应出电压v1和v2以及它们的相关联的电流i1和i2。可以沿着信号路由线标准化在相反方向上的感应电流i1和i2。当使用本发明的水平电感器以允许信号路由线与pcb的表面相邻时,可以消除磁场噪声耦合。因此,可以消除对禁用区的需要,并且可以通过使用用于定位常规垂直电感器的支撑板来实现更小的接触焊盘占用面积。

[0027] 图11示出了根据本公开的一个方面的具有至少一个vr模块1101(vrm)的示例性计算设备1100。应当理解,vrm 1101可以表示vr模块的阵列。vrm 1101可以具有至少一个水平电感器(未示出)。在各种实现中,计算设备1100可以是膝上型计算机、上网本、笔记本、超

级本、智能电话、平板计算机、个人数字助理(pda)、超移动pc、移动电话、台式计算机、服务器、打印机、扫描仪、监视器、机顶盒、娱乐控制单元、数字相机、便携式音乐播放器、或数字视频记录器。在一方面,计算设备1100可以是移动计算设备。在另外的实现中,计算设备1100可以是处理数据的任何其他电子设备。

[0028]

在另一方面,计算设备1100可以具有诸如母板的板,该板具有若干组件,包括但不限于可以或可以不物理地和电气地耦合到这样的母板的半导体处理器。其他组件可包括但不限于易失性存储器(例如dram)、非易失性存储器(例如rom)、闪存、图形处理器、数字信号处理器、密码处理器、通信芯片、芯片组、天线、显示器、触屏控制器、电池、音频编解码器、视频编解码器、功率放大器、全球定位系统(gps)设备、指南针、盖革计数器、加速度计、陀螺仪、扬声器、相机、以及大容量存储设备(诸如硬盘驱动器、压缩盘(cd)、数字多功能盘(dvd)等等)。例如在上面阐述的其他组件中使用一个或多个水平电感器在本公开的范围内。

[0029] 根据本公开,使用水平电感器的计算设备可以包括多个通信芯片。通信芯片还可以根据全球移动通信系统(gsm)、通用分组无线业务(gprs)、通用移动电信系统(umts)、高速分组接入(hspa)、演进hspa(e-hspa)或lte网络来操作。通信芯片可以根据gsm演进的增强型数据(edge)、gsm edge无线电接入网(geran)、通用陆地无线电接入网(utran)或演进型utran(e-utran)来操作。通信芯片可以根据码分多址(cdma)、时分多址(tdma)、数字增强无绳电信(dect)、演进数据优化(ev-do)、其衍生物、以及被称为3g、4g、5g及以上的任何其他无线协议来操作。在其他方面,通信芯片可以根据其他无线协议进行操作。例如,第一通信芯片可以专用于诸如wi-fi和蓝牙的较短距离无线通信,而第二通信芯片可以专用于诸如gps、edge、gprs、cdma、wimax、lte、ev-do等之类的较长距离无线通信。

[0030]

在另一方面,通信芯片可以实现用于向计算设备1100和从计算设备1100传输数据的无线通信。术语“无线”及其衍生物可被用于描述可通过使用调制电磁辐射经由非固态介质来传送数据的电路、设备、系统、方法、技术、通信信道等。该术语并不意味着相关联的设备不包含任何线材,尽管在一些方面它们可能不包含任何线材。

[0031] 通信芯片可以以若干无线标准或协议中的任何标准或协议来实现,包括但不限于电气和电子工程师协会(ieee)标准,包括wi-fi(ieee 502.11族)、ieee 502.16标准(例如ieee 502.16-2005修订)、长期演进(lte)项目以及任何修改、更新和/或修订(例如高级lte项目、超移动宽带(umb)项目(也称为“3gpp2”)等)。兼容ieee 502.16的bwa网络通常被称为wimax网络,wimax网络是代表微波接入全球互通的首字母缩写词,其是通过ieee 502.16标准的一致性和互操作性测试的产品的认证标志。

[0032]

图12示出了根据本公开的一个方面的示例性方法的简化流程图1200。在这个方面,如在第一操作1202中所述,板布局提供了可以在从电路板表面起的第二层中形成的多个信号路由线。在第二部分1204中,具有至少一个水平电感器的至少一个电压调节器模块可以通过信号路由线耦合到电路板。在第三部分1206中,水平电感器可以被定位或具有生成定向地跟随信号路由线的中心磁场线的结构。在第四部分1208中,电路板可以位于计算设备中。

[0033]

在印刷电路板的布局中使用水平电感器的方法的上述方面旨在是非限制性的。对于本领域普通技术人员来说,显然可以在不脱离本公开范围的情况下修改前述方法。

[0034] 为了更容易理解和付诸实践,现在将通过示例的方式描述用于特定方面的本发

明的方法和设备。为了简洁起见,可以省略对特征和属性的重复性描述。

[0035]

示例示例1可以包括一种电路板,具有:在从所述电路板的表面起的第二层中的多个信号路由线;以及至少一个电感器,其耦合到所述电路板且定位在所述信号路由线之上,所述电感器被配置成产生定向地跟随所述信号路由线的磁场线。

[0036]

示例2可以包括示例1和/或本文公开的任何其他示例的电路板,其中,所述至少一个电感器还包括线圈线,所述线圈线具有与所述电路板的表面水平地取向的中心轴。

[0037]

示例3可以包括示例2和/或本文公开的任何其他示例的电路板,还包括耦合到所述电路板的支撑板,其用于附接所述电感器并将所述线圈线定位成水平配置。

[0038]

示例4可以包括示例3和/或本文公开的任何其他示例的电路板,其中,所述线圈线从所述支撑板沿着所述中心轴水平地延长。

[0039]

示例5可以包括示例1和/或本文公开的任何其他示例的电路板,其中,所述至少一个电感器还包括:所述线圈线,具有第一端和第二端;以及支撑所述线圈线的第一端的第一连接构件和支撑所述线圈线的第二端的第二连接构件,其中,所述第一连接构件和所述第二连接构件被附接到所述电路板的表面,以将所述线圈线定位成水平配置。

[0040]

示例6可以包括示例1和/或本文公开的任何其他示例的电路板,其中,所述至少一个电感器还包括与所述电路板的表面水平地取向的电感器阵列。

[0041]

示例7可以包括示例6和/或本文公开的任何其他示例的电路板,还包括耦合到所述电路板的支撑板,其用于附接所述电感器阵列以将其线圈线定位成水平配置。

[0042]

示例8可以包括示例7和/或本文公开的任何其他示例的电路板,其中,所述电感器阵列是第一电感器阵列,所述电路板还包括:所述第一电感器阵列,包括第一组延长的线圈线;以及与所述电路板的表面水平地取向的第二电感器阵列,其附接到所述支撑板,所述第二电感器阵列具有第二组延长的线圈线,所述第二组延长的线圈线面向所述第一电感器阵列的所述第一组延长的线圈线的相反的方向。

[0043]

示例9可以包括示例2和/或本文公开的任何其他示例的电路板,其中,所述至少一个电感器还包括:围绕所述线圈线的壳体材料;以及壳体支撑件,所述壳体支撑件定位在所述壳体材料与所述电路板之间。

[0044]

示例10可以包括一种计算设备,具有:电路板,具有在从所述电路板的表面起的第二层中的多个信号路由线;以及电压调节器模块,具有耦合到所述电路板的至少一个电感器,所述电感器被定位在所述信号路由线之上,并且被配置成产生定向地跟随所述信号路由线的磁场线。

[0045]

示例11可以包括示例10和/或本文公开的任何其他示例的计算设备,其中,所述至少一个电感器还包括线圈线,所述线圈线具有与所述电路板的表面水平地取向的中心轴。

[0046]

示例12可以包括示例11和/或本文公开的任何其他示例的计算设备,还包括耦合到所述电路板的支撑板,其用于附接所述电感器并将所述线圈线定位成水平配置。

[0047]

示例13可以包括示例12和/或本文公开的任何其他示例的计算设备,其中,所述线圈线从所述支撑板沿着所述中心轴水平地延长。

[0048]

示例14可以包括示例10和/或本文公开的任何其他示例的计算设备,其中,所述电感器还包括:所述线圈线,具有第一端和第二端;以及支撑所述线圈线的第一端的第一连接

构件和支撑所述线圈线的第二端的第二连接构件,其中,所述第一连接构件和所述第二连接构件被附接到所述电路板的表面,以将所述线圈线定位成水平配置。

[0049]

示例15可以包括示例10和/或本文公开的任何其他示例的计算设备,其中,所述至少一个电感器还包括与所述电路板的表面水平地取向的电感器阵列。

[0050]

示例16可以包括示例15和/或本文公开的任何其他示例的计算设备,还包括耦合到所述电路板的支撑板,其用于附接所述电感器阵列以将其线圈线定位成水平配置。

[0051]

示例17可以包括示例16和/或本文公开的任何其他示例的计算设备,其中,所述电感器阵列是第一电感器阵列,所述电路板还包括具有第一组延长的线圈线的第一电感器阵列和附接到耦合到所述电路板的第二支撑板的第二电感器阵列。

[0052]

示例18可以包括示例10和/或本文公开的任何其他示例的计算设备,其中,所述至少一个电感器还包括:围绕所述线圈线的壳体材料;以及壳体支撑件,所述壳体支撑件定位在所述壳体材料与所述电路板之间。

[0053]

示例19可以包括一种方法,其针对:形成电路板,所述电路板具有在从所述电路板的表面起的第二层中的多个信号路由线;以及形成电压调节器模块,所述电压调节器模块包括耦合到所述电路板并且被定位在所述信号路由线之上的至少一个电感器,所述电感器被配置成产生定向地跟随所述信号路由线的磁场线。

[0054]

示例20可以包括示例19和/或本文公开的任何其他示例的方法,将支撑板附接到所述电路板,其中,所述至少一个电感器耦合到所述支撑板。

[0055]

应当理解,本文针对特定设备描述的任何属性也可适用于本文描述的任何设备。还应当理解,本文针对特定方法描述的任何属性可适用于本文描述的任何方法。此外,应当理解,对于本文描述的任何设备或方法,不一定将所描述的所有组件或操作都包含在设备或方法中,而是可包含仅一些(但不是所有)组件或操作。

[0056]

术语“包含”应被理解为具有与术语“包括”类似的广义含义,并且应被理解为意味着包括了所述的整体或操作或整体或操作的组,但不排除还有任何其他整体或操作或整体或操作的组。该定义也适用于术语“包含”的变体,例如“包含有”和“包含了”。

[0057]

本文的术语“耦合”(或“连接”)可以理解为电耦合或机械耦合,例如附接或固定或附接,或仅接触而没有任何固定,并且应当理解,可以提供直接耦合或间接耦合(换言之,没有直接接触的耦合)两者。

[0058]

尽管已经参照特定方面具体示出和描述了本公开,但是本领域技术人员应当理解,在不脱离由所附权利要求限定的本公开的范围的情况下,可以在形式和细节上对其进行各种改变。因此,本公开的范围由所附权利要求来指示,并且因此意图涵盖落入权利要求的等效方案的含义和范围内的所有改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1