相变存储单元及其制备方法与流程

本发明涉及半导体,尤其涉及一种相变存储单元及其制备方法。

背景技术:

1、相变存储器(phase change memory,pcm)是一种新型的电阻式非易失性半导体存储器,它以硫系化合物材料为存储介质,利用加工到纳米尺寸的相变材料在晶态(材料呈低阻状态)与非晶态(材料呈高阻状态)时不同的电阻状态来实现数据存储。相变存储器具有非易失性、高速度、高密度、低功耗、高可靠性和与cmos工艺良好的兼容性等明显优势,被国际半导体工业协会认定为最有可能取代闪存成为未来存储器市场主流产品的新型非易失性存储器。

2、相变存储器的典型结构包括底部电极层、顶部电极层及位于底部电极层和顶部电极层之间的相变存储层(gst),底部电极层作为加热器,用于对相变存储层的一小片区域进行加热。底部电极层的加热效果控制着整个相变存储过程,只有提高底部电极层的加热效率以及限制热在器件内部的扩散,才能获得能耗更低、性能更强的器件。

技术实现思路

1、本发明的目的在于提供一种相变存储单元及其制备方法,用于提高底部电极层的加热效率。

2、为了达到上述目的,本发明提供了一种相变存储单元,包括:

3、衬底;

4、介质层,位于所述衬底上;以及,

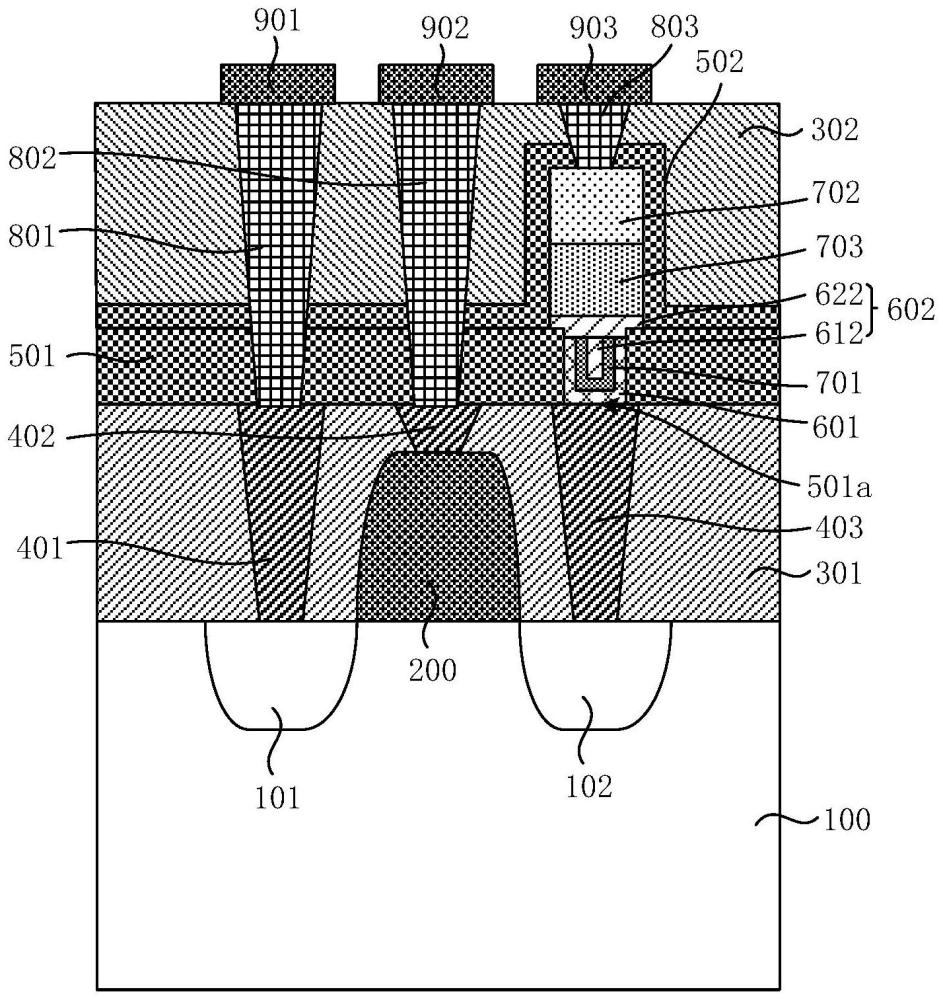

5、堆叠结构,位于所述介质层内,包括由下至上依次设置的第一底部电极层、第二底部电极层、第三底部电极层、相变存储层及顶部电极层,其中,所述第一底部电极层和所述第三底部电极层的电阻率均大于所述第二底部电极层的电阻率。

6、可选的,所述第一底部电极层的电阻率小于所述第三底部电极层的电阻率。

7、可选的,所述第一底部电极层和所述第三底部电极层的材料均包括sic、n型/p型掺杂的sic或tan。

8、可选的,所述第一底部电极层及所述第三底部电极层完全包裹所述第二底部电极层的外壁。

9、可选的,所述第一底部电极层呈u型,所述第二底部电极层位于所述第一底部电极层的开口内,且填充所述第一底部电极层的开口的至少部分深度,所述第三底部电极层覆盖所述第一底部电极层及所述第二底部电极层的顶面。

10、可选的,所述第一底部电极层及所述第二底部电极层均呈u型且依次堆叠,所述第三底部电极层填充在所述第二底部电极层的开口内并延伸覆盖所述第一底部电极层及所述第二底部电极层的顶面。

11、可选的,所述第一底部电极层、所述第二底部电极层及所述第三底部电极层均呈平板状且依次堆叠。

12、可选的,还包括隔热层,所述隔热层位于所述介质层内,且至少覆盖所述堆叠结构裸露的外壁。

13、可选的,所述隔热层的材料包括sicn或si3n4。

14、可选的,所述介质层包括由下至上依次设置的第一子介质层和第二子介质层,所述隔热层位于所述第一子介质层和所述第二子介质层之间,且包括第一子隔热层和第二子隔热层;以及,

15、所述第一子隔热层覆盖所述第一子介质层,且所述第一子隔热层内具有一穿孔,所述第一底部电极层及所述第二底部电极层填充所述穿孔的部分深度,所述第三底部电极层至少填充所述穿孔的剩余深度,所述第二子隔热层覆盖所述第一子隔热层以及覆盖所述第三底部电极层、所述相变存储层及所述顶部电极层裸露的外壁。

16、可选的,还包括:

17、源区和漏区,位于所述衬底内;

18、栅极结构,位于所述源区和所述漏区之间的衬底上;以及,

19、第一焊盘、第二焊盘和第三焊盘,位于所述介质层上,并分别通过位于所述介质层内的第一插塞、第二插塞及第三插塞与所述源区、所述栅极结构及所述顶部电极层电性连接,所述第二底部电极层通过所述第一底部电极层及位于所述介质层内的第四插塞与所述漏区电性连接。

20、本发明还提供了一种相变存储单元的制备方法,包括:

21、提供衬底;

22、形成介质层于所述衬底上;以及,

23、形成堆叠结构于所述介质层内,所述堆叠结构包括由下至上依次设置的第一底部电极层、第二底部电极层、第三底部电极层、相变存储层及顶部电极层,其中,所述第一底部电极层和所述第三底部电极层的电阻率均大于所述第二底部电极层的电阻率。

24、可选的,形成所述介质层及所述堆叠结构的步骤包括:

25、依次形成第一子介质层及第一子隔热层于所述衬底上,所述第一子隔热层中具有一穿孔;

26、依次形成第一底部电极层、所述第二底部电极层及所述第三底部电极层于所述穿孔内,以及依次形成所述相变存储层及所述顶部电极层于所述第三底部电极层上;

27、形成第二子隔热层于所述第一子隔热层上,所述第二子隔热层还覆盖所述第三底部电极层、所述相变存储层及所述顶部电极层裸露的外壁;以及,

28、形成第二子介质层于所述第二子隔热层上,所述第一子介质层及所述第二子介质层构成所述介质层,所述第一子隔热层及所述第二子隔热层构成隔热层。

29、可选的,形成第一底部电极层、所述第二底部电极层、所述第三底部电极层、所述相变存储层及所述顶部电极层的步骤包括:

30、依次形成第一底部电极层、所述第二底部电极层及第一子电极层于所述穿孔的至少部分深度中,所述第一底部电极层及所述第二底部电极层均呈u型并依次覆盖所述穿孔的内壁,所述第一子电极层填充在所述第二底部电极层的开口内;

31、形成第二子电极层于所述第一子隔热层上,所述第二子电极层还填充所述穿孔的剩余深度;以及,

32、形成所述相变存储层及所述顶部电极层于所述第二子电极层上,并同步去除所述顶部电极层、所述相变存储层及所述第二子电极层的部分横向宽度,剩余的所述第一子电极层及所述第二子电极层构成所述第三底部电极层。

33、可选的,形成第一底部电极层、所述第二底部电极层、所述第三底部电极层、所述相变存储层及所述顶部电极层的步骤包括:

34、形成所述第一底部电极层于所述穿孔的至少部分深度中,所述第一底部电极层呈u型并覆盖所述穿孔的内壁;

35、形成所述第二底部电极层于所述第一底部电极层的开口内,所述第二底部电极层填充所述第一底部电极层的开口的至少部分深度;

36、形成第三底部电极层于所述第一子隔热层上及所述穿孔的剩余深度中;以及,

37、形成所述相变存储层及所述顶部电极层于所述第三底部电极层上,并同步去除所述顶部电极层、所述相变存储层及所述第三底部电极层的部分横向宽度。

38、可选的,形成第一底部电极层、所述第二底部电极层、所述第三底部电极层、所述相变存储层及所述顶部电极层的步骤包括:

39、依次形成所述第一底部电极层和所述第二底部电极层于所述穿孔的至少部分深度中;

40、形成第三底部电极层于所述第一子隔热层上及所述穿孔的剩余深度中;以及,

41、形成所述相变存储层及所述顶部电极层于所述第三底部电极层上,并同步去除所述顶部电极层、所述相变存储层及所述第三底部电极层的部分横向宽度。

42、可选的,所述衬底中具有源区和漏区,形成所述第一子介质层之前,还在所述源区和所述漏区之间的衬底上形成栅极结构,并在形成所述第一子介质层之后,在所述第一子介质层内形成分别与所述源区、所述栅极结构及所述漏区电性连接的第一子插塞、第二子插塞及第四插塞,所述穿孔对准并露出所述第四插塞;

43、在形成所述第二子介质层之后,在所述第二子介质层内形成分别与所述第一子插塞、所述第二子插塞及所述顶部电极层电性连接的第三子插塞、第四子插塞及第三插塞;以及,

44、形成第一焊盘、第二焊盘和第三焊盘于所述第二子介质层上,所述第一焊盘、所述第二焊盘和所述第三焊盘分别与所述第三子插塞、所述第四子插塞及所述第三插塞电性连接,所述第一子插塞与所述第三子插塞构成第一插塞,所述第二子插塞与所述第四子插塞构成第二插塞。

45、在本发明提供的相变存储单元中,包括衬底、介质层及堆叠结构,所述介质层位于所述衬底上,所述堆叠结构位于所述介质层内,且包括由下至上依次设置的第一底部电极层、第二底部电极层、第三底部电极层、相变存储层及顶部电极层。本发明中,所述第一底部电极层和所述第三底部电极层的电阻率均大于所述第二底部电极层的电阻率,因此所述第一底部电极层和所述第三底部电极层相较于所述第二底部电极层导热性更差,保温性更好,由于所述第二底部电极层夹在所述第一底部电极层与所述第三底部电极层之间,所述第一底部电极层和所述第三底部电极层可以防止热量扩散,提高整体底部电极的加热效率,减小功耗。相应的,本发明还提供了所述相变存储单元的制备方法。

- 还没有人留言评论。精彩留言会获得点赞!