存储器件及其制造方法与流程

本技术涉及半导体器件的,具体涉及一种存储器件及其制造方法。

背景技术:

1、半浮栅器件通常由一个浮栅晶体管和隧穿晶体管组成,通过隧穿晶体管的沟道对浮栅晶体管的浮栅进行写入和擦除操作。在半浮栅器件中,浮栅晶体管的浮栅与隧穿晶体管的沟道之间存在开口,开口处通常会形成接触界面,界面缺陷在一定程度上限制了器件性能。

技术实现思路

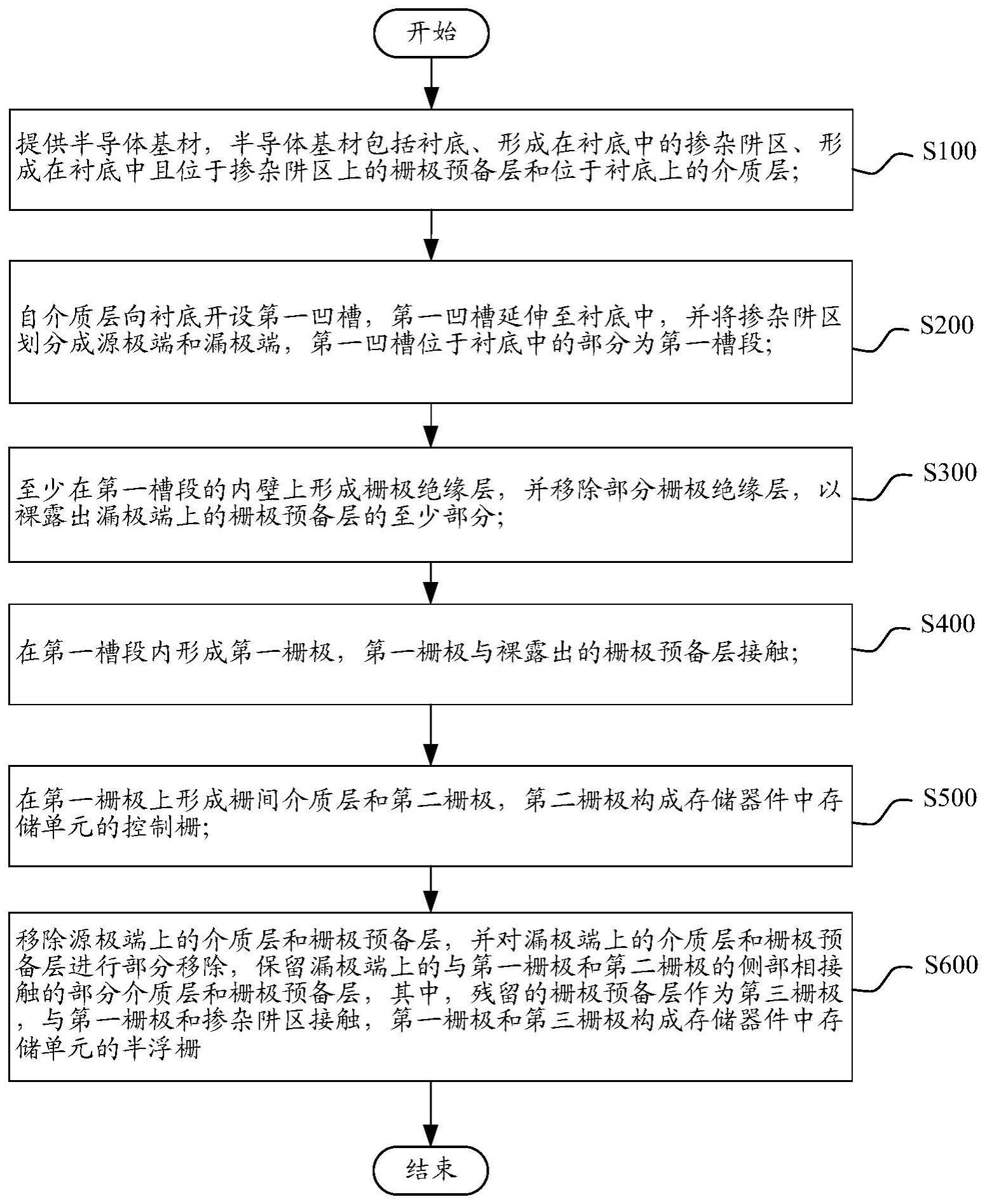

1、本技术一方面提供了一种存储器件的制造方法,包括:提供半导体基材,半导体基材包括衬底、形成在衬底中的掺杂阱区、形成在衬底中且位于掺杂阱区上的栅极预备层和位于衬底上的介质层;自介质层向衬底开设第一凹槽,第一凹槽延伸至衬底中,并将掺杂阱区划分成源极端和漏极端,第一凹槽位于衬底中的部分为第一槽段;至少在第一槽段的内壁上形成栅极绝缘层,并移除部分栅极绝缘层,以裸露出漏极端上的栅极预备层的至少部分;在第一槽段内形成第一栅极,第一栅极与裸露出的栅极预备层接触;在第一栅极上形成栅间介质层和第二栅极,第二栅极构成存储器件中存储单元的控制栅;移除源极端上的介质层和栅极预备层,并对漏极端上的介质层和栅极预备层进行部分移除,保留漏极端上的与第一栅极和第二栅极的侧部相接触的部分介质层和栅极预备层,其中,残留的栅极预备层作为第三栅极,与第一栅极和掺杂阱区接触,第一栅极和第三栅极构成存储器件中存储单元的半浮栅。

2、可选地,提供半导体基材,包括:提供衬底,其中,衬底包括具有第一掺杂类型的掺杂阱区;在衬底上形成第一介质层;对衬底进行第二掺杂类型离子注入,以在掺杂阱区上形成栅极预备层;在第一介质层上形成第二介质层。

3、可选地,至少在第一槽段的内壁上形成栅极绝缘层,并移除部分栅极绝缘层,以裸露出漏极端上的栅极预备层的至少部分,包括:形成栅极绝缘层,其中,栅极绝缘层至少形成在第一槽段的内壁上;在第一凹槽内填充介质材料;刻蚀介质材料和栅极绝缘层,以裸露出漏极端上的栅极预备层的至少部分。

4、可选地,至少在第一槽段的内壁上形成栅极绝缘层,并移除部分栅极绝缘层,以裸露出漏极端上的栅极预备层的至少部分,还包括:利用第一凹槽中的栅极绝缘层对第一凹槽底部的衬底进行第二掺杂类型离子注入。

5、可选地,介质材料包括富含硅的复合材质或者多晶硅材质。

6、可选地,在第一槽段内形成第一栅极,包括:在第一凹槽内形成第一栅极材料层;

7、对第一凹槽内的第一栅极材料层进行部分移除,保留第一槽段内的第一栅极材料层,以作为第一栅极,其中,第一栅极与暴露出的漏极端上的栅极预备层接触,且第一栅极藉由残留的栅极绝缘层与衬底的其他部分隔离。

8、可选地,在第一槽段内形成第一栅极,还包括:移除第一凹槽内未被第一栅极覆盖的栅极绝缘层。

9、可选地,在第一栅极上形成栅间介质层和第二栅极,包括:形成栅间介质层,其中,栅间介质层覆盖第一凹槽的未被第一栅极所覆盖的内壁,并覆盖第一栅极;在栅间介质层上形成填充于第一凹槽内的第二栅极材料层,作为第二栅极。

10、可选地,介质层包括层叠设置的第一介质层和第二介质层,第一介质层和第二介质层的材质不同;移除源极端上的介质层和栅极预备层,并对漏极端上的介质层和栅极预备层进行部分移除,保留漏极端上的与第一栅极和第二栅极的侧部相接触的部分介质层和栅极预备层,包括:形成掩膜图案层,其中,掩膜图案层至少覆盖漏极端上的介质层,且掩膜图案层与第一介质层的材质相同;移除源极端上的第二介质层;移除源极端上的第一介质层和掩膜图案层;移除源极端上的栅极预备层;对漏极端上的介质层和栅极预备层进行刻蚀,移除漏极端上的介质层和栅极预备层的部分,保留与第一栅极和第二栅极的侧部相接触的部分介质层和栅极预备层。

11、可选地,该方法还包括形成隔离挡墙。

12、可选地,半导体基材还包括用于隔离存储器件中存储单元的浅沟槽隔离结构,浅沟槽隔离结构沿存储器件中字线延伸的第一方向间隔分布,并沿存储器件中位线延伸的第二方向延伸。

13、可选地,自介质层向衬底开设第一凹槽,包括:移除介质层的部分,以形成第一凹槽的第二槽段,并移除浅沟槽隔离结构的相应部分以形成第二凹槽;在第二槽段的基础上,进一步移除衬底的相应部分,以形成第一槽段,第一槽段和第二槽段构成第一凹槽。

14、可选地,在第一槽段内形成第一栅极之后,方法还包括:对浅沟槽隔离结构上的第二凹槽进行进一步地移除,以加宽加深第二凹槽;其中,在第一栅极上形成第二栅极材料层以作为第二栅极时,加宽加深的第二凹槽也填充有第二栅极材料层,以作为在第一方向上连接存储单元的控制栅的字线连接线。

15、本技术所提供的存储器件的制造方法具有以下有益效果:

16、第一,由于栅极预备层和掺杂阱区都是在衬底中形成的,栅极预备层和掺杂阱区具有连续的晶格构造,因此,由该制造方法制造得到的存储器件中,第三栅极与掺杂阱区具有连续的晶格构造,即,第三栅极与掺杂阱区的连接界面处的晶格是完整的,有利于降低界面缺陷,提高存储器件的性能。

17、第二,由于第一栅极和第二栅极都是通过填充第一凹槽形成的,因此,能够自动实现第一栅极和第二栅极的大致对齐,有利于提升存储器件性能、降低工艺难度。

18、本技术另一方面提供了一种存储器件,存储器件包括:基体,包括衬底及形成在衬底中,且位于衬底一侧的掺杂阱区;第一基体凹槽,自掺杂阱区向下延伸,第一基体凹槽的内壁上形成有栅极绝缘层;第一栅极,填充在第一基体凹槽中,并至少部分凸出于掺杂阱区之外;栅间介质层,形成在第一栅极上;第二栅极,形成在栅间介质层上,第二栅极作为存储器件中存储单元的控制栅;第三栅极,形成在掺杂阱区上,且与第一栅极接触,共同构成存储器件中存储单元的半浮栅,其中,第三栅极与掺杂阱区具有连续的晶格构造。

19、可选地,存储器件还包括形成在第三栅极上的介质层,介质层包括层叠设置的第一介质层和第二介质层;其中,第一介质层和第二介质层的材质不同。

20、可选地,基体还包括用于隔离存储器件中存储单元的浅沟槽隔离结构,浅沟槽隔离结构在基体中沿存储器件中字线延伸的第一方向间隔分布,并沿存储器件中位线延伸的第二方向延伸。

21、可选地,浅沟槽隔离结构凸出于掺杂阱区,且浅沟槽隔离结构的远离衬底的一侧高于第一栅极的远离衬底的一侧;浅沟槽隔离结构的远离衬底的一侧表面开设有第二基体凹槽,第二基体凹槽内填充有导电材料,以在第一方向上将存储单元的控制栅连接在一起;其中,第二栅极与填充在第二基体凹槽内的导电材料具有相同的材质。

22、可选地,第二栅极与第一栅极宽度相同,且彼此对齐。

23、可选地,第二基体凹槽的底部低于第一栅极的远离衬底的一侧;第二基体凹槽的宽度大于第二栅极的宽度。

24、可选地,第一隔离挡墙,形成在第一栅极、栅间介质层、及第二栅极的背离第三栅极的一侧;第二隔离挡墙,形成在第三栅极背离第一栅极、栅间介质层、及第二栅极的一侧。

25、本技术所提供的存储器件中,第三栅极形成在掺杂阱区上,且与第一栅极接触,共同构成存储器件中存储单元的半浮栅。其中,第三栅极与掺杂阱区具有连续的晶格构造,即,第三栅极与掺杂阱区的连接界面处的晶格是完整的,有利于降低界面缺陷,提高存储器件的性能。

- 还没有人留言评论。精彩留言会获得点赞!