一种半导体器件、制备方法以及芯片与流程

本技术涉及半导体,尤其涉及一种半导体器件、制备方法以及芯片。

背景技术:

1、沟槽型半导体结构由于没有平面型结构的jfet(junction field-effecttransistor,结型场效应晶体管)区,而具有更高的电流密度和更低的导通损耗而成为目前的主流趋势。

2、为了减小栅极电容,提高沟槽型半导体结构的开关速率,同时为了进一步降低导通损耗,沟槽型半导体结构中经常设计有第二沟槽栅(dummy gate)结构,当电流密度过大时会导致沟槽型半导体结构因存在寄生晶体管而易发生闩锁效应,且由于第二沟槽栅结构的存在,更容易使沟槽型半导体结构中的寄生晶体管导通,而导致栅极失去控制作用,从而增加发生闩锁效应的概率。

技术实现思路

1、本技术提供一种半导体器件、制备方法以及芯片,用于提供一种能够在保证半导体器件的其他参数不变的情况下,有效改善半导体器件闩锁效应,提升器件的可靠性的技术方案。

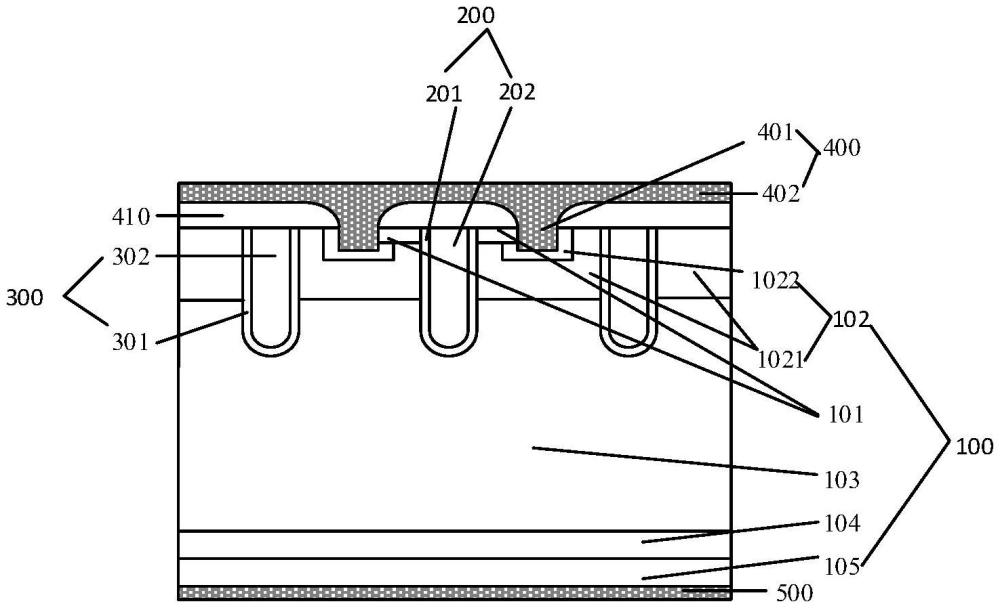

2、第一方面,本技术提供一种半导体器件,包括:

3、基底;

4、第一沟槽栅,第一沟槽栅设置于基底内;

5、第二沟槽栅,第一沟槽栅设置于基底内,并与第一沟槽栅间隔设置;

6、第一导电类型源区,第一导电类型源区设置于基底内,并与所述第一沟槽栅的至少一侧的部分侧壁相连接,以在所述半导体器件导通时,所述基底中从所述第二沟槽栅的至少一侧通过的载流子的浓度大于,从所述第一沟槽栅的至少一侧通过的载流子的浓度。

7、在一种可选的实施方式中,所述半导体器件还包括:第二导电类型掺杂区;

8、沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型掺杂区设置于所述第一沟槽栅和所述第二沟槽栅之间。

9、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型掺杂区与所述第一沟槽栅、所述第二沟槽栅相连接。

10、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二导电类型掺杂区与所述第一导电类型源区相连接。

11、在一种可选的实施方式中,所述半导体器件还包括第一电极;

12、沿所述基底的厚度方向,所述第一电极设置于所述基底的第一侧的。

13、在一种可选的实施方式中,所述第一电极具有延伸至所述基底内的延伸部;

14、沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述延伸部设置于所述第一沟槽栅和所述第二沟槽栅之间。

15、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述延伸部设置于所述第一沟槽栅的两侧,所述第一导电类型源区与所述第一沟槽栅的两侧的部分侧壁相连接。

16、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述延伸部设置于所述第一沟槽栅的一侧,所述第一导电类型源区与靠近所述延伸部一侧的所述第一沟槽栅的部分侧壁相连接。

17、在一种可选的实施方式中,所述第一导电类型源区与靠近所述第一沟槽栅一侧的所述延伸部的至少部分侧壁相连接。

18、在一种可选的实施方式中,所述第二导电类型掺杂区与所述延伸部靠近所述第二沟槽栅一侧的侧壁相连接。

19、在一种可选的实施方式中,所述第二导电类型掺杂区与所述延伸部的至少部分底部相连接。

20、在一种可选的实施方式中,所述第一导电类型源区与所述延伸部的部分底部相连接;

21、所述第二导电类型掺杂区与所述延伸部的部分底部相连接。

22、在一种可选的实施方式中,所述第二导电类型掺杂区包括第二导电类型接触区;

23、沿所述基底的厚度方向,所述第二导电类型接触区与所述延伸部的至少部分底部相连接。

24、在一种可选的实施方式中,所述第二导电类型接触区与所述第一导电类型源区相连接。

25、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型接触区与所述延伸部的部分侧壁相连接。

26、在一种可选的实施方式中,所述第二导电类型接触区与所述延伸部的全部底部相连接。

27、在一种可选的实施方式中,所述第二导电类型接触区与靠近所述第一沟槽栅一侧的所述延伸部的部分侧壁。

28、在一种可选的实施方式中,所述第二导电类型接触区与靠近所述第二沟槽栅一侧的所述延伸部的全部侧壁相连接。

29、在一种可选的实施方式中,所述第二导电类型接触区与靠近所述第一沟槽栅一侧的所述延伸部的部分侧壁相连接。

30、在一种可选的实施方式中,所述第二导电类型接触区与靠近所述第二沟槽栅一侧的所述延伸部的部分侧壁相连接。

31、在一种可选的实施方式中,所述第二导电类型接触区与靠近所述第一沟槽栅一侧的所述延伸部的部分底部相连接。

32、在一种可选的实施方式中,所述第二导电类型接触区与靠近所述第一沟槽栅一侧的所述延伸部的部分侧壁相连接。

33、在一种可选的实施方式中,所述第二导电类型掺杂区还包括第二导电类型阱区;

34、沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与所述第一沟槽栅、所述第二沟槽栅以及所述第二导电类型接触区均连接。

35、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二导电类型阱区与所述第二导电类型接触区和所述第一导电类型源区均连接。

36、在一种可选的实施方式中,所述第二导电类型阱区与远离所述第一电极的一侧的所述第二导电类型接触区相连接。

37、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二导电类型阱区与所述第二导电类型接触区的底面相连接。

38、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二导电类型阱区与所述第一导电类型源区的底面相连接。

39、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与所述第二导电类型接触区的至少部分侧面相连接。

40、在一种可能的实现方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与所述第一沟槽栅的部分侧壁相连接。

41、在一种可能的实现方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与所述第二沟槽栅的部分侧壁相连接。

42、在一种可选的实施方式中,所述第二导电类型阱区与靠近所述第一沟槽栅一侧的所述第二导电类型接触区的部分侧面相连接。

43、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二沟槽栅与所述延伸部的一侧相连接。

44、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二沟槽栅与所述延伸部的部分底部相连接。

45、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与靠近所述第二沟槽栅一侧的所述第二导电类型接触区的至少部分侧面相连接。

46、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与靠近所述第一沟槽栅一侧的所述第二导电类型接触区的部分侧面相连接。

47、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与靠近所述第二沟槽栅一侧的所述第二导电类型接触区的全部侧面相连接。

48、在一种可选的实施方式中,所述第二导电类型掺杂区还包括第二导电类型重掺杂区;

49、沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型重掺杂区设置于所述延伸部和所述第二沟槽栅之间。

50、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型重掺杂区与所述延伸部和所述第二沟槽栅均连接。

51、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二导电类型重掺杂区与所述第二导电类型阱区和所述第二导电类型接触区均连接。

52、在一种可选的实施方式中,所述第二导电类型重掺杂区与靠近所述第二沟槽栅的所述延伸部的部分侧壁相连接。

53、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与靠近所述第一沟槽栅一侧的所述第二导电类型接触区部分侧面相连接。

54、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与靠近所述第二沟槽栅一侧的所述第二导电类型接触区的部分侧面相连接。

55、在一种可选的实施方式中,所述第二导电类型重掺杂区的掺杂离子浓度大于所述第一导电类型源区的掺杂离子浓度。

56、在一种可选的实施方式中,所述第二导电类型重掺杂区的掺杂离子浓度为1018~1021cm-3,和/或,所述第一导电类型源区的掺杂离子浓度为1018~1021cm-3。

57、在一种可选的实施方式中,所述第二导电类型阱区的离子掺杂浓度小于所述第二导电类型接触区的离子掺杂浓度。

58、在一种可选的实施方式中,所述第二导电类型阱区的离子掺杂浓度为1016~1018cm-3,和/或,所述第二导电类型接触区的离子掺杂浓度为1018~1021cm-3。

59、在一种可选的实施方式中,所述半导体器件还包括第一导电类型漂移区(103);

60、所述第一导电类型漂移区设置于所述基底内,并设置于所述第二导电类型阱区背离所述第一电极的一侧。

61、在一种可选的实施方式中,所述第一导电类型漂移区覆盖所述第一沟槽栅和所述第二沟槽栅的底部和部分侧壁。

62、在一种可选的实施方式中,所述第一导电类型漂移区的离子掺杂浓度为1013~1015cm-3。

63、在一种可选的实施方式中,所述半导体器件还包括第二电极;

64、沿所述基底的厚度方向,所述第二电极设置于所述基底的第二侧,并位于所述第一导电类型漂移区背离所述第二导电类型阱区的一侧。

65、在一种可选的实施方式中,所述半导体器件还包括第一导电类型缓冲区(104);

66、所述第一导电类型缓冲区设置于所述基底内,并设置在所述第一导电类型漂移区与所述第二电极之间。

67、在一种可选的实施方式中,所述半导体器件还包括第二导电类型集电区(105);

68、第二导电类型集电区设置在所述第一导电类型缓冲区和所述第二电极之间。

69、在一种可选的实施方式中,所述第二导电类型集电区的离子掺杂浓度为1018~1021cm-3。

70、在一种可选的实施方式中,所述第一导电类型缓冲区的离子掺杂浓度为1014~1016cm-3。

71、在一种可选的实施方式中,所述半导体器件还包括隔离层;

72、沿所述基底的厚度方向,所述隔离层设置于所述基底的第一侧,并至少设置于所述第一沟槽栅和所述第二沟槽栅与所述第一电极之间。

73、在一种可选的实施方式中,所述第一导电类型中的导电离子n型离子,所述第二导电类型中的导电离子为p型离子;

74、或,所述第一导电类型中的导电离子为p型离子,所述第二导电类型中的导电离子为n型离子。

75、第二方面,本技术还提供了一种半导体器件的制备方法,所述方法包括:提供基底;

76、形成第一沟槽栅和第二沟槽栅;所述第一沟槽栅和所述第二沟槽栅间隔设置于所述基底内;

77、形成第一导电类型源区;所述第一导电类型源区设置于所述基底内,并与所述第一沟槽栅的至少一侧的部分侧壁相连接,以在所述半导体器件导通时,所述基底中从所述第二沟槽栅的至少一侧通过的载流子的浓度大于,从所述第一沟槽栅的至少一侧通过的载流子的浓度。

78、在一种可选的实施方式中,所述形成第一沟槽栅和第二沟槽栅包括:

79、在所述基底的第一侧对所述基底进行刻蚀,以在所述基底中形成沟槽结构;

80、在所述沟槽结构中形成所述第一沟槽栅和所述第二沟槽栅。

81、在一种可选的实施方式中,在所述形成第一沟槽栅和第二沟槽栅之后,所述方法还包括:

82、从所述基底的第一侧,对所述基底进行至少两次离子注入,形成第二导电类型掺杂区;沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型掺杂区设置于所述第一沟槽栅和所述第二沟槽栅之间。

83、在一种可选的实施方式中,沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型掺杂区与所述第一沟槽栅、所述第二沟槽栅均连接。

84、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二导电类型掺杂区与所述第一导电类型源区相连接。

85、在一种可选的实施方式中,在所述形成第一导电类型源区之前,从所述基底的第一侧,对所述基底进行至少两次离子注入,形成第二导电类型掺杂区包括:

86、从所述基底的第一侧,对所述基底进行第一次离子注入,形成第二导电类型阱区。沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型阱区与所述第一沟槽栅、所述第二沟槽栅以及所述第二导电类型接触区均连接。

87、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二导电类型阱区与所述第二导电类型接触区和所述第一导电类型源区均连接。

88、在一种可选的实施方式中,所述形成第一导电类型源区包括:

89、从所述基底的第一侧的第一指定区域,对所述基底进行第二次离子注入,形成所述第一导电类型源区。

90、在一种可选的实施方式中,在形成第一导电类型源区之后,所述方法还包括:

91、沿所述基底的厚度方向,在所述基底的第一侧形成第一电极;

92、所述第一电极具有延伸至所述基底内的延伸部;沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述延伸部位于所述第一沟槽栅和所述第二沟槽栅之间。

93、在一种可选的实施方式中,所述在所述基底的第一侧形成第一电极包括:

94、在所述基底的第一侧形成隔离层;

95、至少在所述隔离层和所述基底中形成接触孔;

96、在所述隔离层上以及所述接触孔中形成所述第一电极。

97、在一种可选的实施方式中,在所述隔离层和所述基底中形成接触孔之后,在所述隔离层上以及所述接触孔中形成所述第一电极之前,所述从所述基底的第一侧,对所述基底进行至少两次离子注入,形成第二导电类型掺杂区还包括:

98、沿所述基底的厚度方向,从所述基底的第一侧,对所述基底进行第三次离子注入,形成第二导电类型接触区;

99、沿所述基底的厚度方向,所述第二导电类型接触区与所述延伸部的至少部分底部和所述第一导电类型源区均连接。

100、在一种可选的实施方式中,从所述基底的第一侧,对所述基底进行第三次离子注入,形成第二导电类型接触区之后,所述从所述基底的第一侧,对所述基底进行至少两次离子注入,形成第二导电类型掺杂区还包括:

101、沿所述基底的厚度方向,从所述基底的第一侧的第二指定区域,对所述基底进行第四次离子注入,形成第二导电类型重掺杂区;

102、沿所述第一沟槽栅和所述第二沟槽栅的间隔方向,所述第二导电类型重掺杂区与所述延伸部和所述第二沟槽栅相连接。

103、在一种可选的实施方式中,沿所述基底的厚度方向,所述第二导电类型重掺杂区与所述第二导电类型阱区和所述第二导电类型接触区均连接。

104、在一种可选的实施方式中,所述方法还包括:

105、沿所述基底的厚度方向,在所述基底的第二侧形成第二电极。

106、在一种可选的实施方式中,在所述基底的第二侧形成第二电极之前,所述方法还包括:

107、从所述基底的第二侧,对所述基底进行第五次离子注入以形成第一导电类型缓冲区;

108、第一导电类型缓冲区位于所述第一导电类型漂移区与所述第二电极之间。

109、在一种可选的实施方式中,从所述基底的第二侧,对所述基底依次进行第五次离子注入之后,在所述基底的第二侧形成第二电极之前,所述方法还包括:

110、从所述基底的第二侧,对所述基底进行第六次离子注入,以形成第二导电类型集电区;

111、所述第二导电类型集电区位于所述第二电极和所述第一导电类型缓冲区之间。

112、第三方面,本技术实施例还提供了一种芯片,包括第一方面任一项所述的半导体器件。

113、本技术提供的技术方案中,只在第一沟槽栅的至少一侧设置第一导电类型源区,故本技术中的半导体器件在第二沟槽栅附近不会形成寄生晶体管,且由于第一导电类型源区产生的电场的作用,使得该半导体器件导通时大部分载流子从第二沟槽栅附近流过,小部分载流子从第一沟槽栅附近流过,此时,不会导致第一沟槽栅附近的寄生晶体管导通,很大程度上解决了半导体器件在大电流密度下易发生闩锁的问题,提升了器件的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!