一种通信芯片及数据处理方法与流程

1.本技术涉及通信技术领域,尤其涉及一种通信芯片及数据处理方法。

背景技术:

2.随着5g通信技术的发展,高速率、高质量的数据传输成为芯片设计必须要考虑的重要问题。当需求的网络速率超过物理器件的承载能力时,多通道并行传输以实现高速率接口的方式是大势所趋。

3.为保证数据传输的质量,通信芯片的物理编码子层(physical coding sublayer,pcs)在数据高速率传输时通常选择里德所罗门前向纠错式(rs-forward error correction,rs-fec)的编码方式。rs-fec需要发送侧在数据中插入对齐标识(am),数据经过光纤或电缆传输后,接收侧在数据流中寻找am用于数据同步对齐。

技术实现要素:

4.本技术实施例提供了一种通信芯片以及数据处理方法,可以实现各种速率配置组合的数据对齐需求,可以减少逻辑资源的占用和浪费,实现结构优化。

5.本技术实施例提供了一种通信芯片,包括:多个同步模块、一套缓存模块和多个对齐模块;

6.其中,所述同步模块,被设置为接收对应通道的数据,并对接收的所述数据进行同步,并将同步后的数据存入缓存模块;

7.所述缓存模块包括多个先入先出队列fifo;所述fifo,被设置为缓存对应同步模块输出的同步后的数据;

8.所述对齐模块中,被设置为将所述缓存模块中的对应通道同步后的数据进行对齐,并将对齐的数据合并输出。

9.本技术实施例提供了一种数据处理方法,所述方法应用于本技术提供的通信芯片,所述方法包括:

10.通过每个同步模块接收对应通道上的数据,并对接收的所述数据进行同步,并将同步后的数据存入缓存模块;

11.通过缓存模块中的每个先入先出队列fifo缓存对应同步模块输出的同步后的数据;

12.通过多个对齐模块中的至少一个对齐模块,将所述缓存模块中的所有通道同步后的数据进行对齐,并将对齐的数据合并输出。

13.本技术实施例提供的技术方案,可以包括多个同步模块、一套缓存模块以及多个对齐模块,其中,一套缓存模块包括多个fifo,fifo缓存对应同步模块输出的同步后的数据,通过至少一个对齐模块将缓存模块中至少一个fifo缓存的所有通道同步的数据进行对齐,并合并输出,可以通过多个fifo实现各种速率配置组合的数据对齐需求,可以减少逻辑资源的占用和浪费,实现结构优化。

附图说明

14.图1是本技术实施例提供的一种通信芯片的结构示意图;

15.图2是本技术实施例提供的一种数据处理方法流程图;

16.图3是本技术实施例提供的一种配置速率下的数据流示意图;

17.图4是本技术实施例提供的一种配置速率下的数据流示意图;

18.图5是本技术实施例提供的一种配置速率下的数据流示意图;

19.图6是本技术实施例提供的一种配置速率下的数据流示意图;

20.图7是本技术实施例提供的一种配置速率下的数据流示意图;

具体实施方式

21.为保证数据传输的质量,通信芯片的物理编码子层(physical coding sublayer,pcs)在数据高速率传输时通常选择里德所罗门前向纠错式(rs-fec)的编码方式。rs-fec需要发送侧在数据中插入同步对齐标识(am),数据经过光纤或电缆传输后,接收侧在数据流中寻找am用于数据同步对齐。

22.相关技术中,通信芯片接收的数据同步对齐方式不能兼容多种协议和速率,导致通信芯片的使用不灵活,通信芯片研发、使用成本大大增加。

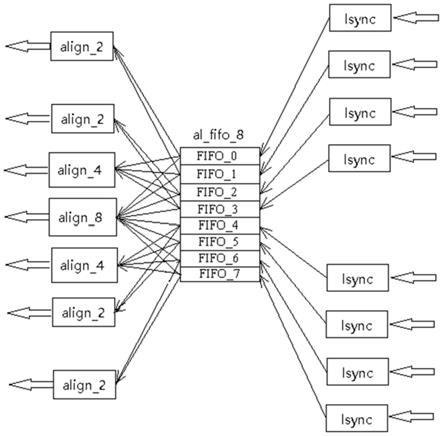

23.图1是本技术提供的一种通信芯片的结构示意图,其中,本技术提供的通信芯片包含物理编码子层(physical coding sublayer,pcs),并且支持rs-fec配置的环境。

24.如图1所示,本技术提供的通信芯片包括多个同步模块(lsync)、一套缓存模块(al_fifo_8)和多个对齐模块(包括align_2,align_4,align_8)。

25.其中,同步模块,被设置为接收对应通道的数据,并对接收的数据进行同步,并将同步后的数据存入缓存模块;缓存模块包括多个先入先出队列fifo;fifo,被设置为缓存对应同步模块输出的同步后的数据;对齐模块中,被设置为将缓存模块中的对应通道同步后的数据进行对齐,并将对齐的数据合并输出。其中,合并输出是指合并后输出。

26.在一个示例性的方式中,同步模块的数量为8个,所述对齐模块的数量为7个;fifo的数量为8个,如图1所示,缓存模块(al_fifo_8)可以包括8个fifo,分别是fifo_0,fifo_1,fifo_2,fifo_3,fifo_4,fifo_5,fifo_6,fifo_7。由多个同步模块输出的同步后的数据依次缓存至fifo中,同步模块与fifo可以一一对应。

27.需要说明的是同步模块的数量与fifo的数量可以相同,同步模块和fifo的数量还可以是其他数量,可以根据实际需要进行设置,对齐模块的数量也可以是其他数量。

28.在一个示例性的方式中,多个对齐模块输出数据的速率不完全相同。具体的,多个对齐模块支持的每次输出数据的大小不完全相同,或者多个对齐模块数据的支持数据不完全相同。

29.在一个示例性的方式中,多个对齐模块包括4个第一对齐模块(align_2),2个第二对齐模块(align_4)和1个第三对齐模块(align_8);

30.其中,所述第一对齐模块,被设置为将两个fifo对应缓存的两条通道同步后的数据进行对齐,并将所述两条通道同步后的数据合并输出;

31.所述第二对齐模块,被设置将4个fifo对应缓存的4条通道同步后的数据进行对齐,并将所述4条通道同步后的数据合并输出;

32.所述第三对齐模块,被设置为将8个fifo对应缓存的8条通道同步后的数据进行对齐,并将所述8条通道同步后的数据进行合并输出。

33.具体的,如图1所示,同步模块(lsync)可以是单通道同步模块,可以是完成一个前向纠错fec模式的通道(lane)的同步状态机,支持所有以太网速率。第一对齐模块(align_2),可以是两条通道数据的对齐模块,可以是完成速率为50ge(gigabit ethernet),且2个feclane的对齐状态机,可以完成2个fec lane上数据类型(symbol)的合并功能。第二对齐模块(align_4)可以是四条通道数据的对齐模块,可以是完成速率为100ge,且4个fec lane的对齐状态机,可以完成4个fec lane上的symbol的合并功能。第三对齐模块(align_8),可以是8条通道数据的对齐模块,可以是完成速率为200ge,且8个fec lane的对齐状态机,可以完成8个fec lane上symbol的合并功能。

34.在本技术实施例中,数据源可以是从pcs发送侧rs-fec编码后的输出数据,且已经按照不同fce lane分为n路(可以是1-8)的数据,即n条通道上的数据。其中,若数据传输的速率为25ge,则包含1个fec lane的数据,若数据传输的速率为50ge,则包含2个fec lane的数据;若数据传输的大小为100ge,则包含4个fec lane的数据;若数据传输的速率为200ge,则包含8个fec lane的数据。

35.本技术提供的通信芯片进行数据处理的过程如下:

36.如图1所示,同步模块进行数据同步:输入的n条通道上的数据,即输入的n路数据经过对应的同步模块,分别完成n路数据的单fec lane同步过程。具体同步的过程是,使用发送时pcs协议中固定周期产生并且携带在pcs处理数据流中的对齐标识(am),查询数据中的对齐标识,将对齐标识之前的数据去掉,将对齐标识作为传输数据的边界。具体可以参考相关技术,具体可以参考ieee 802.3-2018clause82、91、108、119、134等章节。同步模块将对应通道的数据实现同步后,输出同步信号(携带同步状态信息)和通道标识(fec lane号)给配置速率对应的对齐模块,并将同步后的数据给缓存模块。

37.缓存模块解偏斜:缓存模块包括8个fifo,n路(可以是8路)fec lane同步后的数据直接写入对应的fifo中。每个fifo中的读取和清空操作可以由下游的对齐模块(第一对齐模块,第二对齐模块或者第三对齐模块)来进行控制。

38.对齐模块进行数据对齐:根据端口的配置速率,第一对齐模块(align_2),第二对齐模块(align_4)或第三对齐模块(align_8)通过控制上游的fifo读和清空操作实现多条fec lane数据的对齐。具体的是:在缓存模块中的n个fifo已经缓存与配置速率对应的全部通道同步后的数据的情况下,向对齐模块发送通知消息,对齐模块接收到该通知消息以及对应的同步状态信息,同时读取n个fifo中同步后的数据,以实现数据的对齐,并按照通道标识进行排序后输出。其中,第一对齐模块(align_2)完成速率为50ge的数据对齐,第二对齐模块(align_4)完成速率为100ge的数据对齐,第三对齐模块(align_8)完成速率为200ge的数据对齐。其中,端口的配置速率可以理解为端口配置的支持速率。

39.需要说明的是,本技术提供的通信芯片并不局限于图1所示的结构形式,其中,同步模块、缓存模块中fifo的数量以及对齐模块的数量等可以根据实际需要进行调整。

40.本技术提供的通信芯片,可以完成对来自物理媒介适配层(physical media attachment,pma)的数据进行同步、对齐操作,可以支持多种速率的配置方式,可以支持以外网和cpri多种速率的配置和组合,从而呈现多种端口支持速率的配置方式,例如可以是

支持4个25ge速率,或者4个50ge速率,或者支持4个通用公共无线接口(cpri)的端口,或者支持2个100ge速率的端口,或者支持1个速率100ge以及2个25ge/50ge/cpri的端口,或者支持1个速率200ge的端口。

41.本技术提供的通信芯片,可以包括多个同步模块、一套缓存模块以及多个对齐模块,其中,一套缓存模块包括多个fifo,fifo缓存对应同步模块输出的同步后的数据,通过至少一个对齐模块将缓存模块中至少一个fifo缓存的所有通道同步的数据进行对齐,并合并输出,可以通过多个fifo实现各种速率配置组合的数据对齐需求,可以减少逻辑资源的占用和浪费,实现结构优化。在一个实施方式中,缓存模块包括8个fifo,通过8个fifo实现各种速率配置组合的数据对齐需求,若不适用本技术提供的通信芯片,则需要24个fifo才能实现相同的功能,从而可以减少逻辑资源的占用和浪费,优化芯片,降低成本。

42.图2是本技术实施例提供的一种数据处理方法,所述方法应用于本技术提供的通信芯片,该芯片可以是包含pcs的芯片,如图2所示,本技术实施例提供的技术方案包括:

43.s210:通过同步模块接收对应通道上的数据,并对接收的所述数据进行同步,并将同步后的数据存入缓存模块。

44.s220:通过缓存模块中的每个先入先出队列fifo缓存对应同步模块输出的同步后的数据。

45.s230:通过多个对齐模块中的至少一个对齐模块,将所述缓存模块中的所有通道同步后的数据进行对齐,并将对齐的数据合并输出。

46.其中,具体数据通信方式可以参考通过通信芯片进行通信的方法。

47.在一个示例性的方式中,多个所述对齐模块数据的速率不完全相同。

48.在一个示例性的方式中,所述同步模块的数量为8个,所述对齐模块的数量为7个;所述fifo的数量为8个。

49.在一个示例性的方式中,所述方法还包括:通过所述同步模块将同步状态信息以及通道标识发送给配置速率对应的对齐模块;在所述缓存模块缓存与配置速率对应的全部通道同步后的数据的情况下,向所述配置速率对应的对齐模块发送通知消息;

50.所述将所述缓存模块中的所有通道同步后的数据进行对齐,并将对齐的数据合并输出,包括:在接收到所述同步状态信息以及所述通知消息的情况下,读取所述缓存模块中fifo缓存的对应通道的同步后的数据,并基于所述通道标识将读取的数据进行排列并输出。

51.其中,每条通道上的数据可以是由pcs发送侧同时发送的,由于每条通道数据传输过程中可能通过的物理介质并不相同,会存在某些通道上的数据接收会存在延迟,为了实现各条通道的数据对齐,同步模块将对应通道的数据进行同步后,缓存至缓存模块中对应的fifo中,在全部通道同步后的数据均缓存至对应的fifo的情况下,对齐模块同时读取非空的fifo中的数据,实现数据的对齐。

52.具体的,在对齐模块接收到同步状态信息的情况下,可以判断对接收的数据进行了同步,在对齐模块接收到通知消息的情况下,可以判断缓存模块已经缓存了与配置速度对应的全部通道同步后的数据,从而对齐模块在接收到同步状态信息和通知消息的情况下,同时读取缓存模块中非空的fifo,实现将所有通道数据进行对齐,并按照通道标识将读取的数据进行排列,从而使输出的数据按照数据发送的顺序进行输出。

53.在一个示例性的方式中,还包括:在每两条通道同步后的数据之间的时间偏斜超过设定范围的情况下,通过对齐模块对缓存模块中的fifo进行清空,并返回通过每个同步模块接收对应通道上的数据,并对接收的所述数据进行同步,并将同步后的数据存入缓存模块的操作。

54.其中,时间偏斜可以是指时间之间的间隔,设定范围可以根据实际情况进行设置。在每两条通道同步后的数据之间的时间偏斜超过设定范围的情况下,则fifo发生上溢,数据对齐失败,需要将非空的fifo进行复位,重新开始同步对齐过程。

55.其中,本技术实施例中,具体数据处理方法可以参考通过通信芯片进行处理的方法。

56.如图1所示,同步模块进行数据同步:输入的n条通道上的数据,即输入的n路数据经过对应的同步模块,分别完成n路数据的单fec lane同步过程。具体同步的过程是,使用发送时pcs协议中固定周期产生并且携带在pcs处理数据流中的对齐标识(am),查询数据中的对齐标识,将对齐标识之前的数据去掉,将对齐标识作为传输数据的边界。具体可以参考相关技术,具体可以参考ieee 802.3-2018clause82、91、108、119、134等章节。同步模块将对应通道的数据实现同步后,输出同步信号(携带同步状态信息)和通道标识(fec lane号)给配置速率对应的对齐模块,并将同步后的数据给缓存模块。

57.缓存模块解偏斜:缓存模块包括8个fifo,n路(可以是8路)fec lane同步后的数据直接写入对应的fifo中。每个fifo中的读取和清空操作可以由下游的对齐模块(第一对齐模块,第二对齐模块或者第三对齐模块)来进行控制。

58.对齐模块进行数据对齐:根据端口的配置速率,第一对齐模块(align_2),第二对齐模块(align_4)或第三对齐模块(align_8)通过控制上游的fifo读和清空操作实现多条fec lane数据的对齐。具体的是:在缓存模块中的n个fifo已经缓存与配置速率对应的全部通道同步后的数据的情况下,向对齐模块发送通知消息,对齐模块接收到该通知消息以及对应的同步状态信息,同时读取n个fifo中同步后的数据,以实现数据的对齐,并按照通道标识进行排序后输出。其中,第一对齐模块(align_2)完成速率为50ge的数据对齐,第二对齐模块(align_4)完成速率为100ge的数据对齐,第三对齐模块(align_8)完成速率为200ge的数据对齐。其中,端口的配置速率可以理解为端口配置的支持速率。

59.其中,如图1所示,以第三对齐模块(align_8)为例,数据对齐具体操作如下:

60.步骤一:复位后第三对齐模块(align_8)清空缓存模块(al_fifo_8)中的8个fifo;

61.步骤二:当某条通道(个数小于8条时)同步后,对应的fifo只写不读;

62.步骤三:当8条通道都同步且8个fifo都非空时,缓存模块(al_fifo_8)开始同时读取8个fifo中同步后的数据,首次读出的就是am;

63.步骤四:当任意一个fifo发生上溢时,说明通道之间的时间偏斜超过容许范围,对齐失败,此时第三对齐模块(align_8)复位全部8个fifo,重新开始同步对齐过程。

64.步骤五:对齐成功后,根据同步模块给的fec lane号对8路输入数据按顺序重新排列后输出。

65.其中,第一对齐模块(align_2),第二对齐模块(align_4)的对齐过程和第三对齐模块(align_8)类似,区别是第一对齐模块(align_2)从对应的2个fifo输入数据并控制这2个fifo的读和清空操作,第二对齐模块(align_4)从对应的4个fifo输入数据并控制这4个

fifo的读和清空操作。

66.在一个示例性的方式中,在配置速率为一个通道的数据速率的情况下,通过每个所述同步模块接收对应通道上的数据,并对接收的所述数据进行同步,并将同步后的数据发送至下游的接收侧。具体的,如图3所示,一个通道的数据速率为25ge,配置速率包括4个25ge;通过4个同步模块对应接收4个通道上的数据,并对接收的数据进行同步,将同步后的数据发送至下游的接收侧,即同步后的数据不经过缓存模块和对齐模块。原因在于:由于配置速率为一个通道的数据速率相同,不需要将至少两条通道同步后的数据进行合并输出,故同步模块输出的数据可以直接发送至下游接收侧。

67.在一个示例性的方式中,在配置速率为两条通道的数据速率之和,且多个对齐模块分别对应接收8条通道上的数据的情况下,

68.通过多个对齐模块中的至少一个对齐模块,将所述缓存模块中的所有通道同步后的数据进行对齐,并将对齐的数据合并输出,包括:

69.通过4个第一对齐模块,将缓存模块中8个fifo对应缓存的8条通道同步后的数据进行对齐,并将对齐的数据合并输出;其中,每个第一对齐模块,被设置为将缓存模块中两个fifo对应缓存的两道通道同步后的数据进行对齐,并将所述两条通道同步后的数据合并输出。

70.具体的,如图4所示,一个通道的数据速率为25ge,配置速率包括:4个50ge,通过8个同步模块(lsync)对应接收8个通道上的数据,并对接收的数据进行同步,将同步后的数据缓存至对应的8个fifo中;通过4个第一对齐模块(align_2)将8个fifo中缓存的同步后的数据进行对齐,并将对齐的数据进行合并输出,其中,每个第一对齐模块(align_2)将2个fifo中缓存的同步后的数据进行对齐,并合并输出。

71.在一个示例性的实施方式中,在配置速率为4条通道的数据速率之和,且多个对齐模块接收8条通道上的数据的情况下,通过多个对齐模块中的至少一个对齐模块,将所述缓存模块中的所有通道同步后的数据进行对齐,并将对齐的数据合并输出,包括:

72.通过两个第二对齐模块,将缓存模块中8个fifo对应缓存的8条通道同步后的数据进行对齐,并将对齐的数据合并输出;其中,每个第二对齐模块,被设置为将缓存模块中4个fifo对应缓存的4条通道同步后的数据进行对齐,并将所述4条通道同步后的数据合并输出。

73.具体的,如图5所示,一个通道的数据速率为25ge,配置速率包括2个100ge,通过8个同步模块(lsync)对应接收8个通道上的数据,并对接收的数据进行同步,将同步后的数据缓存至对应的8个fifo中;通过2个第二对齐模块(align_4)将8个fifo中缓存的8条通道的同步后的数据进行对齐,并将对齐的数据进行合并输出,其中,每个第二对齐模块(align_4)将4个fifo中缓存的2条通道同步后的数据进行对齐,并合并输出。

74.在一个示例性的实施方式中,在配置速率包括4条通道的数据速率之和,以及两条通道的数据速率,且多个对齐模块接收8条通道上的数据的情况下,

75.通过多个对齐模块中的至少一个对齐模块,将所述缓存模块中的所有通道同步后的数据进行对齐,并将对齐的数据合并输出,包括:通过1个第二对齐模块,将缓存模块中4个fifo对应缓存的4条通道同步后的数据进行对齐,通过两个第一对齐模块,将缓存模块中另外4个fifo对应缓存的4条通道同步后的数据进行对齐,将同步后的数据合并输出。

76.具体的,如图6所示,一个通道的数据速率为25ge,配置速率包括1个100ge和2个50ge,通过8个同步模块(lsync)对应接收8个通道上的数据,并对接收的数据进行同步,将同步后的数据缓存至对应的8个fifo中;通过1个第二对齐模块(align_4)将4个fifo中缓存的4条通道同步后的数据进行对齐,并将4个fifo中4条通道同步后的数据进行合并输出,并且同时通过2个第一对齐模块(align_2)将另外4个fifo中缓存的4条通道同步后的数据进行对齐,并将另外4个fifo中4条通道同步后的数据进行合并输出。

77.在一个示例性的实施方式中,在配置的传输速率为8条通道的传输速率之和,且多个对齐模块接收8条通道上的数据的情况下,通过多个对齐模块中的至少一个对齐模块,将所述缓存模块中的所有通道同步后的数据进行对齐,并将对齐的数据合并输出,包括:

78.通过1个第三对齐模块,将缓存模块中8个fifo对应缓存的8条通道同步后的数据进行对齐,并所述8条通道同步后的数据合并输出;其中,第三对齐模块,被设置为将缓存模块中8个fifo对应缓存的8条通道同步后的数据进行对齐,并将所述8条通道同步后的数据合并输出。

79.具体的,如图7所示,一个通道的数据速率为25ge,配置速率包括1个200ge,通过8个同步模块(lsync)对应接收8个通道上的数据,并对接收的数据进行同步,将同步后的数据缓存至对应的8个fifo中;通过1个第三对齐模块(align_8)将8个fifo中缓存的8条通道同步后的数据进行对齐,并将8个fifo缓存的8条通道同步后的数据进行合并输出。

80.需要说明的是图1,图2-图7中,箭头的流向为数据的流向,图2-图7中,带有箭头的曲线流向为不同配置速率下真实的数据流向。

81.本技术提供的技术方案可以支持多种以太网速率的配置和组合,通信芯片中只包含一套缓存模块,其中,缓存模块可以包括8个fifo,在数据处理过程中,可以使通信芯片既可以灵活配置,使用,又可以节约电路逻辑资源,降低通信芯片面积和功耗。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1