数据接收电路以及半导体装置的制作方法

本公开实施例涉及半导体,特别涉及一种数据接收电路以及半导体装置。

背景技术:

1、在存储器应用中,随着信号传输速率越来越快以及时钟频率的增大,输入数据信道损耗对信号质量的影响越来越大,容易导致码间干扰(isi,intersymbolinterference)。isi是指由于输入数据信道的带宽的限制而引起的先前传输的输入数据影响当前传输的输入数据的传输的现象。目前通常利用均衡电路对输入数据信道进行补偿,以期降低码间干扰带来的不良影响,均衡电路可以选择ctle(continuous time linearequalizer,连续线性均衡电路)或dfe(decision feedback equalizer,判决反馈均衡电路)。

2、然而,目前采用的均衡电路相对复杂,影响输入数据传输速度。

技术实现思路

1、本公开实施例提供一种数据接收电路以及半导体装置,至少有利于在降低码间干扰问题的同时,减小电路复杂度,提升输入数据传输速度。

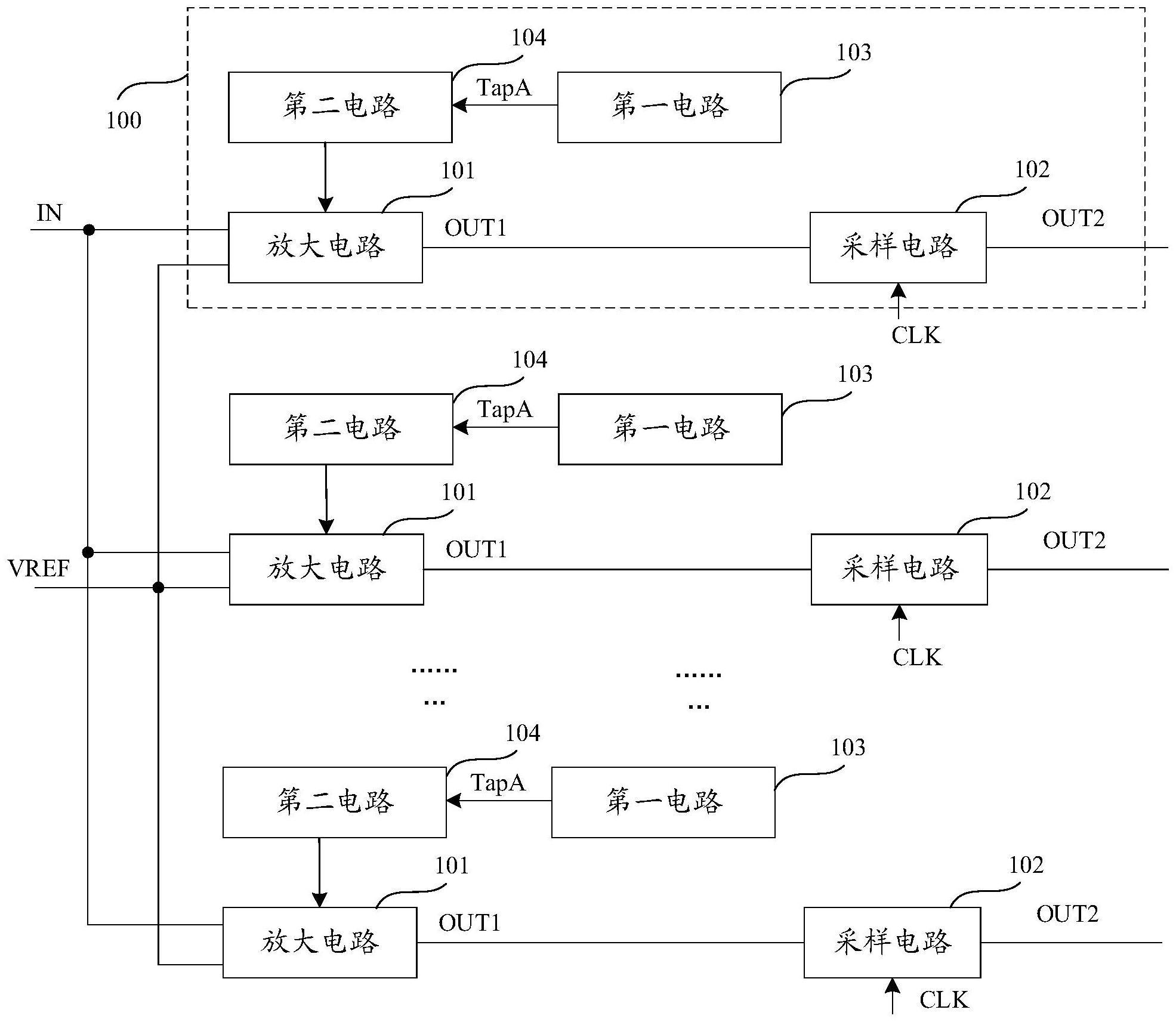

2、根据本公开一些实施例,本公开实施例一方面提供一种数据接收电路,包括:多条数据路径,所述多条数据路径均接收输入数据和采样时钟,且每条所述数据路径接收的所述采样时钟的相位不同,所述多条数据路径包括:按自然数递增编号的第1数据路径至第m数据路径,第i数据路径为所述多条数据路径中的任一条所述数据路径,1≤i≤m,m≥2,且所述第1数据路径至所述第m数据路径中,任意两个编号连续的所述数据路径接收的所述采样时钟之间的相位差相同;其中,所述第i数据路径包括:放大电路,被配置为,放大所述输入数据的电压以及参考电压之间的压差并输出第一信号对;采样电路,被配置为,接收相应的所述采样时钟,对所述第一信号对进行采样并输出第二信号对;第一电路,被配置为,接收n条所述数据路径输出的所述第二信号对,基于接收到的所有所述第二信号对,输出相应的抽头控制信号,所述抽头控制信号为多比特信号,n≤m;第二电路,被配置为,接收所述抽头控制信号,并响应于所述抽头控制信号,以与所述抽头控制信号相对应的调节值调整所述第i数据路径中的所述第一信号对的电平。

3、在一些实施例中,第i数据路径的所述第一电路接收除第i-1数据路径以外的至少两条所述数据路径输出的所述第二信号对,所述第1数据路径的所述第一电路接收除所述第m数据路径以外的至少两条所述数据路径输出的所述第二信号对;其中,1<i≤m,m≥3。

4、在一些实施例中,第i-1数据路径的所述第一电路接收所述第i-1数据路径输出的所述第二信号对以及所述第i数据路径输出的所述第二信号对;所述第m数据路径的所述第一电路接收所述第1数据路径输出的所述第二信号对以及所述第m数据路径输出的所述第二信号对。

5、在一些实施例中,所述第m数据路径的所述第一电路接收所述第1数据路径输出的所述第二信号对以及第2数据路径输出的所述第二信号对;所述第i-1数据路径的所述第一电路接收所述第i数据路径输出的所述第二信号对和第i+1数据路径输出的所述第二信号对,i+1<m;第m-1数据路径的所述第一电路接收所述第1数据路径输出的所述第二信号对以及所述第m数据路径输出的所述第二信号对。

6、在一些实施例中,m为4,所述相位差为90°。

7、在一些实施例中,第i数据路径的所述第一电路接收包括所述第i数据路径输出的所述第二信号对,所述第1数据路径的所述第一电路接收包括第1数据路径输出的所述第二信号对;其中,1<i≤m,m≥3。

8、在一些实施例中,n=m。

9、在一些实施例中,所述第二信号对包括第二数据信号和第二互补数据信号,所述第二数据信号和所述第二互补数据信号互为反相信号,所述第二数据信号用于表征接收到的所述输入数据;所述抽头控制信号包括第一控制信号和第二控制信号,所述调节值包括第一调节值和第二调节值,所述第一控制信号与所述第一调节值相对应,所述第二控制信号与所述第二调节值相对应,且所述第一控制信号和所述第二控制信号均为多比特信号;其中,所述第一电路还被配置为:基于接收到的所有所述第二数据信号,输出相应的所述第一控制信号;基于接收到的所有所述第二互补数据信号,输出相应的所述第二控制信号。

10、在一些实施例中,所述第一电路还被配置为,接收置零信号以及n个抽头信号,其中,一所述抽头信号与一所述第二信号对相对应;任一所述第二信号对中,所述第二数据信号与第一子信号相对应,所述第二互补数据信号与第二子信号相对应,所述第一子信号为所述置零信号以及所述抽头信号中的一者,所述第二子信号为所述置零信号以及所述抽头信号中的另一者;其中,所述第一控制信号为,将接收到的所有所述第二数据信号对应的所述第一子信号进行加法运算得到;所述第二控制信号为,将接收到的所有所述第二互补数据信号对应的所述第二子信号进行加法运算得到。

11、在一些实施例中,所述置零信号的每一比特数据均为0,所述抽头信号的至少一比特数据为1;若所述第二数据信号为0,所述第二互补数据信号为1,则所述第一子信号为所述置零信号,所述第二子信号为所述抽头信号;若所述第二数据信号为1,所述第二互补数据信号为0,则所述第一子信号为所述抽头信号,所述第二子信号为所述置零信号。

12、在一些实施例中,所述第一电路还被配置为:基于接收到的所有所述第二数据信号,选择所述置零信号和/或从n个所述抽头信号中调用相应的所述抽头信号作为所述第一子信号,并将选择的所有所述第一子信号进行加法运算,以输出所述第一控制信号;基于接收到的所有所述第二互补数据信号,选择所述置零信号和/或从n个所述抽头信号中调用相应的所述抽头信号作为所述第二子信号,并将选择的所有所述第二子信号进行加法运算,以输出所述第二控制信号。

13、在一些实施例中,所述数据接收电路还包括:n个模式寄存器,每一所述抽头信号存储于相应的所述模式寄存器内。

14、在一些实施例中,所述数据接收电路还包括:寄存器,所述寄存器内存储有多个不同的所述第一控制信号以及多个不同的所述第二控制信号;所述第一电路包括:选择器,被配置为,基于接收到的所有所述第二数据信号从所述寄存器内调用相应的所述第一控制信号,并向所述第一电路提供所述第一控制信号,基于接收到的所述第二互补数据信号从所述寄存器内调用相应的所述第二控制信号,并向所述第一电路提供所述第二控制信号。

15、在一些实施例中,所述数据接收电路还包括:加法器,被配置为,获取2n个所述抽头控制信号并将所述抽头控制信号存储至所述寄存器内;其中,每一所述抽头控制信号为对n个所述置零信号以及n个所述抽头信号中任意选择n个信号进行加法运算,且不同的所述抽头控制信号基于不同的n个所述信号进行加法运算得到。

16、在一些实施例中,所述第一信号对包括第一数据信号和第一参考数据信号,所述放大电路包括第一节点和第二节点,所述第一节点输出所述第一数据信号,所述第二节点输出所述第一参考数据信号;所述第二电路包括:第一控制电路,连接于所述第一节点和地端之间,根据所述第二控制信号导通或关闭,且所述第一控制电路在导通期间以所述第二调节值调整所述第一信号对的电平;第二控制电路,连接于所述第二节点和所述地端之间,根据所述第一控制信号导通或关闭,且所述第二控制电路在导通期间以所述第一调节值调整所述第一信号对的电平。

17、在一些实施例中,所述第一控制电路包括:多个并联的第一nmos管,每一所述第一nmos管的栅极接收所述第二控制信号中一比特数据,所述第一nmos管连接在所述第一节点与所述地端之间;所述第二控制电路包括:多个并联的第二nmos管,每一所述第二nmos管的栅极接收所述第一控制信号中一比特数据,所述第二nmos管连接在所述第二节点与所述地端之间。

18、在一些实施例中,所述第i数据路径还包括:第一调节电路,被配置为,接收第i-1数据路径输出的所述第二信号对,并响应于接收到的所述第二信号对调整所述第i数据路径中的第一信号对,其中,若所述第i数据路径为所述第1数据路径则所述第i-1数据路径为所述第m数据路径。

19、在一些实施例中,所述第一调节电路包括:第一开关电路以及第一补偿电路,所述第一开关电路连接在所述放大电路与所述第一补偿电路之间,所述第一开关电路根据接收到的所述第二信号对导通或关闭,且所述第一开关电路导通期间,所述第一补偿电路接收第一抽头信号并以与所述第一抽头信号相对应的调节值调整所述第一信号对。

20、在一些实施例中,所述第i数据路径还包括:第二调节电路,被配置为,接收第i-2数据路径输出的所述第二信号对,并响应于接收到的所述第二信号对调整所述第i数据路径中的所述第一信号对,其中,若所述第i数据路径为第2数据路径则所述第i-2数据路径为所述第m数据路径,若所述第i数据路径为所述第1数据路径则所述第i-2数据路径为第m-1数据路径。

21、在一些实施例中,所述第二调节电路包括:第二开关电路以及第二补偿电路,所述第二开关电路连接在所述放大电路与所述第二补偿电路之间,所述第二开关电路根据接收到的所述第二信号对导通或关闭,且所述第二开关电路导通期间,所述第二补偿电路接收第二抽头信号并以与所述第二抽头信号相对应的调节值调整所述第一信号对。

22、根据本公开另一些实施例,本公开实施例另一方面还提供一种半导体装置,包括前述任一实施例提供的数据接收电路。

23、在一些实施例中,所述半导体装置包括存储芯片。

24、本公开实施例提供的技术方案至少具有以下优点:

25、本公开实施例提供的数据接收电路的技术方案中,多条数据路径接收具有不同相位的采样时钟以传输输入数据;其中,任一条数据路径包括放大电路、采样电路、第一电路以及第二电路,第一电路接收n条数据路径输出的第二信号对,并输出相应的抽头控制信号,抽头控制信号为多比特信号,该抽头控制信号不仅可表征n条数据路径输出的第二信号对对当前传输的输入数据的码间干扰的影响,且抽头控制信号对第一信号对的电平进行调整的调节值还可根据抽头控制信号中不同比特数据的数值调整而改变。因此,本公开实施例中,第二电路响应于抽头控制信号对放大电路输出的第一信号对的电平进行调整,即进行判决反馈均衡,以减小先前传输的输入数据对当前传输的输入数据的影响,保证输入数据传输的准确性,且还可以改变执行判决反馈均衡的步进,使得数据接收电路具有不同的dfe能力。另外,相较于针对每一第二信号对均设计一开关电路以及一补偿电路的方案而言,本公开实施例的第二电路的复杂度更低,且第二电路所需的面积也相应更小,从而有利于减少数据接收电路的负载,提升输入数据传输速率、降低功耗以及传输延迟。

- 还没有人留言评论。精彩留言会获得点赞!