面向跨芯片互连的LVDS并行数据自动校准电路及方法与流程

面向跨芯片互连的lvds并行数据自动校准电路及方法

技术领域

1.本发明涉及多芯系统校准领域,具体涉及一种面向跨芯片互连的lvds并行数据自动校准电路及方法。

背景技术:

2.在高性能计算和大数据应用的背景下,系统架构师需要不断在给定的功率范围内集成更多内核、加速器和内存。而随着集成电路工艺的发展进入后摩尔时代,电子及物理的限制让半导体先进制程的持续微缩与升级难度越来越高。继续通过单芯片实现大型系统的方案必然面临着良率大幅降低、设计和掩模成本急剧增加等问题。将传统的单芯片设计方案改成多芯片进行设计,并利用高速接口进行互连或利用先进封装工艺进行集成的方案成为更优的选择。lvds(low voltage differential signaling)是一种低摆幅的差分信号技术,具有低功耗、低误码率、低串扰和低辐射等优点,可满足跨裸芯之间的高速互连需求。

3.然而多芯片设计在提升系统性能、降低大型系统设计复杂度的同时也会额外引入由跨芯片互连所导致的问题或故障。由于pcb布线以及片间接口部分会引入时钟偏差(time skew),所以lvds并行数据在进行跨芯片传输过程中存在相位漂移以及高低电平占空比不完全相同等问题,可能会导致下游芯片对片间传输数据的采样错误,进而导致数据包错误甚至丢失。

4.针对lvds并行数据存在时序差异导致传输错误的问题,需要通过调整通道延时来达到各数据通道能与时钟通道对齐的目的。传统方式有手动调整各通道延时系数,通过不断试验观测各通道采样结果后,对各通道延时系数进行反复修正,直到并行数据采样完全正确,非常耗时耗力。因此很有必要设计一种全自动校准电路,可以对数据通道对齐状况进行自检并根据检测结果自行调整各通道的延时系数,以此解放人力并实现便捷高效的自动校准效果。

技术实现要素:

5.针对现有技术中的上述不足,本发明提供的面向跨芯片互连的lvds并行数据自动校准电路及方法解决了现有lvds并行数据校准耗时耗力的问题。

6.为了达到上述发明目的,本发明采用的技术方案为:

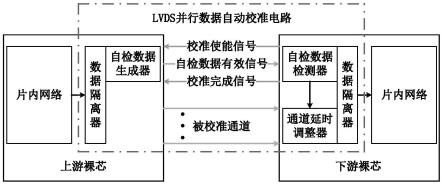

7.提供一种面向跨芯片互连的lvds并行数据自动校准电路,其包括上游裸芯发送端和下游裸芯接收端;上游裸芯发送端包括第一数据隔离器和自检数据生成器;下游裸芯接收端包括第二数据隔离器、自检数据检测器和通道延时调整器;

8.自检数据生成器,用于在校准状态下为每个通道生成确定格式的自检数据,即自检并行数据;

9.自检数据检测器,用于在需要进行校准时生成校准使能信号并发送至上游裸芯发送端;在校准状态下将一段时间内接收到的有效的自检并行数据与已知的自检数据进行比较,获取通道的对齐信息并提交给通道延时调整器;在校准完成后生成校准完成信号并发

送至上游裸芯发送端;

10.通道延时调整器,用于根据通道的对齐信息对时钟通道和数据通道的延时做出相应调整;

11.第一数据隔离器,用于在校准状态下阻止上游裸芯片内数据包流向片间链路;

12.第二数据隔离器,用于在校准状态下阻止自检数据流入下游裸芯片内。

13.进一步地,在各通道调整的延时稳定后,再次通过自检数据检测器接收一段时间的自检数据,获取通道的对齐信息,若仍有数据通道未对齐,则继续通过通道延时调整器调整时钟通道或数据通道的延时。

14.进一步地,上游裸芯发送端的内部信号包括:本地时钟输出以及产生自检数据的时钟、片内输出数据、片内输出数据有效指示、下游裸芯输入通道空闲指示、自检数据输出、自检数据有效指示输出、校准使能信号,以及校准结束信号;

15.上游裸芯发送端处的lvds接口用于:发送时钟、发送片内输出数据或自检数据、发送片内输出数据有效指示信号或自检数据、发送自检数据有效指示信号、接收下游裸芯输入通道空闲指示信号、接收校准使能信号,以及接收校准完成信号;

16.下游裸芯接收端的内部信号包括:外部时钟输入以及采样自检数据的时钟、片间输入数据、片间输入数据有效指示、本地输入通道空闲指示、自检数据输入、自检数据有效指示输入、校准使能信号、校准结束信号、校准成功信号、校准失败信号,以及通道对齐指示;

17.下游裸芯接收端处的lvds接口用于:接收时钟、接收片间输入数据、接收片间输入数据有效指示信号或自检数据、接收自检数据有效指示信号、发送本地输入通道空闲指示信号、发送校准使能信号,以及发送校准完成信号。

18.提供一种面向跨芯片互连的lvds并行数据自动校准方法,其包括面向跨芯片互连的lvds并行数据自动校准系统,还包括以下步骤:

19.s1、将下游裸芯接收端的校准使能信号置1,并将校准使能信号发送至上游裸芯发送端;

20.s2、判断上游裸芯发送端处收到的校准使能信号是否为高,若是则进入步骤s3;否则重复当前步骤;

21.s3、使上游裸芯发送端进入校准状态,阻止上游裸芯片内数据包流向片间链路,产生确定格式的自检数据,同时拉高自检数据有效信号;

22.s4、判断下游裸芯接收端处收到的自检数据有效信号是否为高,若是则进入步骤s5;否则不做处理;

23.s5、使下游裸芯接收端进入校准状态,接收自检数据并阻止自检数据流入下游裸芯片内;

24.s6、将一段时间内接收到的有效的自检并行数据与已知的自检数据进行比较,获取通道的对齐信息并提交给通道延时调整器;

25.s7、根据通道的对齐信息对时钟通道和数据通道的延时做出相应调整;

26.s8、生成校准完成信号并发送至上游裸芯发送端;

27.s9、通过上游裸芯发送端停止产生自检数据,将自检数据有效信号置0并发送至下游裸芯接收端,允许上游裸芯中的片内数据包流向片间链路;

28.s10、判断下游裸芯接收端检测到自检数据有效信号是否为低,若是则允许下游裸芯中的片间数据流向片内,完成自动校准;否则继续阻止下游裸芯中的片间数据流向片内。

29.进一步地,步骤s3中产生确定格式的自检数据的具体方法为:

30.将0和1交替赋值给自检数据的每一位,即让第1~m条lvds通道均交替传输信号0和信号1。

31.进一步地,步骤s6的具体方法包括以下子步骤:

32.s6-1、持续接收有效的自检并行数据,使每个数据通道的有效自检数据采样至少256次;

33.s6-2、获取每个数据通道的错误采样次数:对于每个数据通道,将本次采样数据与上一次采样数据做位同或,若同或结果出现一次1,则判定采样错误1次;

34.s6-3、判断一个数据通道在至少256次采样中的错误采样次数是否超过设定值,若是则判定该数据通道未与时钟通道对齐;否则判定该数据通道与时钟通道为对齐状态。

35.进一步地,步骤s7的具体方法包括以下子步骤:

36.s7-1、根据通道的对齐信息判断是否所有通道都处于对齐状态,若是则进入步骤s8;否则进入步骤s7-2;

37.s7-2、通过调整时钟通道的延时系数获取一个使大于设定数量的数据通道都被正确采样的时钟通道的延时系数;

38.s7-3、分别调整各数据通道延时系数,判断在当前时钟通道的延时系数下是否能实现所有数据通道均被正确采样,若是则将校准成功信号calib_good置1,进入步骤s8;否则进入步骤s7-4;

39.s7-34、判断是否已遍历完所有的通道延时组合,若是则将校准失败信号calib_fail置1,进入步骤s8;否则调整时钟通道的延时系数,返回步骤s7-3。

40.进一步地,步骤s6-3中的设定值为2。

41.本发明的有益效果为:本发明可以在适当的时机自行生成可以突显时序差异问题的检测数据,可以自行根据自检数据采样结果准确的判断各通道对齐状况,再自行按照合适的算法去调整时钟和各数据通道的延时。除此之外,在校准过程中本发明可以主动暂停正常数据包的跨片传输,避免上游裸芯中待跨片传输数据包的丢失或者自检数据流入下游裸芯片内网络影响其正常运行。以上整个过程均不需要人为干预,全由硬件电路自身完成检测并修复,节省了人力。

附图说明

42.图1为本自动校准电路的结构图;

43.图2为本方法的流程示意图。

具体实施方式

44.下面对本发明的具体实施方式进行描述,以便于本技术领域的技术人员理解本发明,但应该清楚,本发明不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本发明的精神和范围内,这些变化是显而易见的,一切利用本发明构思的发明创造均在保护之列。

45.如图1所示,该面向跨芯片互连的lvds并行数据自动校准电路包括上游裸芯发送端和下游裸芯接收端;上游裸芯发送端包括第一数据隔离器和自检数据生成器;下游裸芯接收端包括第二数据隔离器、自检数据检测器和通道延时调整器;

46.自检数据生成器,用于在校准状态下为每个通道生成确定格式的自检数据,即自检并行数据,并将自检数据有效信号置1;

47.自检数据检测器,用于在需要进行校准时生成校准使能信号并发送至上游裸芯发送端;在校准状态下将一段时间内接收到的有效的自检并行数据与已知的自检数据进行比较,获取通道的对齐信息(即数据通道传输的信号是否能被时钟通道传输的时钟正确采样)并提交给通道延时调整器;在校准完成后生成校准完成信号并发送至上游裸芯发送端;

48.通道延时调整器,用于根据通道的对齐信息对时钟通道和数据通道的延时做出相应调整;

49.第一数据隔离器,用于在校准状态下阻止上游裸芯片内数据包流向片间链路;

50.第二数据隔离器,用于在校准状态下阻止自检数据流入下游裸芯片内。

51.在具体实施过程中,校准使能信号和校准完成信号的状态均在接收端产生,并由lvds链路传输至发送端,整个校准电路的运行状态均受这两个信号的控制。当校准使能信号为高且校准完成信号为低时,就代表片间信号传输通道处于校准中。

52.在本发明的一个实施例中,假设需要被校准的通道包括1条传输时钟的通道、77条传输数据的通道和1条传输片间数据有效指示信号的通道,也就是第0~78条通道。上游裸芯发送端内部信号、下游裸芯接收端内部信号、上游裸芯发送端的lvds接口信号和下游裸芯接收端的lvds接口信号的简要说明如表1~4所示。

53.表1:上游裸芯发送端内部信号

[0054][0055]

表2:下游裸芯接收端内部信号

[0056][0057][0058]

表3:上游裸芯发送端lvds接口信号

[0059][0060]

表4:下游裸芯接收端lvds接口信号

[0061][0062][0063]

需要注意的是,od_lanei接口与id_lanei接口之间由第i条lvds通道连接。

[0064]

在本实施例中,自动校准的方法具体可以为:

[0065]

首先将下游裸芯接收端的校准使能信号encalib_rx置1。该信号会由od_lane81经第81条lvds通道传输至id_lane81,然后与上游裸芯发送端的encalib_tx信号连接。

[0066]

当上游裸芯发送端检测到校准使能信号encalib_tx为高时,数据隔离器会阻止片内数据流向片间。具体方法为,将cpiready一直赋0,假定下游裸芯输入通道一直非空闲,这样上游裸芯中待跨片传输的数据包就会先暂存在本地输出通道。同时od_lane1~78将连接到test_data_tx信号,准备传输自检数据。

[0067]

发送端自检数据生成器产生确定格式的自检数据test_data_tx,同时拉高自检数

据有效信号test_valid_tx。自检产生方式为,将78’h0和78’h3fffffffffffffffffff交替赋值给自检数据test_data_tx,即让第1~78条lvds通道均交替传输信号0和信号1。自检数据有效信号将连接到od_lane79,使用第79条lvds通道传输至下游裸芯接收端。

[0068]

下游裸芯接收端检测到自检数据有效信号test_valid_rx为高时,数据隔离器阻止片间数据流向下游裸芯片内。具体方法为,将cpivalid一直赋0,假定片间输入数据无效,这样就能保证接收的自检数据不会影响片内网络。同时id_lane1~78将连接到test_data_rx,id_lane79连接到test_valid_rx,准备接收自检数据。

[0069]

对于同一条通道,对有效的自检数据一共采样至少256次,每次都需要将本次采样数据与上一次采样数据做位同或。如果第n条通道的同或结果为1,说明该条通道本次采样数据与上一次采样数据相同。但由于每条通道均是交替发送信号0和信号1,从而可以证明同或结果为1的通道本次未被时钟通道传输的时钟正确采样。为防止误判通道未对齐,所以只有当一个数据通道在256次采样中采样错误超过2次时,才能认定该数据通道未与时钟通道对齐。在下游裸芯接收端使用78位的align_status寄存器记录本次判断各数据通道对齐状态的结果。

[0070]

如果align_status为78’h0,即所有数据通道都能被正确采样时,则直接生成校准完成信号并发送至上游裸芯发送端,并将校准成功信号calib_good置1。否则先调整时钟通道的延时系数,找到一个能使大部分数据通道都被正确采样的状态,然后再分别调整各数据通道延时系数;如果在该时钟通道延时状态下不能实现所有数据通道均被正确采样,则需要再返回调整时钟通道延时系数;每调整一次时钟或数据通道的延时,都需要重新判断该延时组合是否能使所有的数据通道均被正确采样;如果已经遍历完所有的通道延时组合都不能使全部数据通道同时与时钟通道对齐,则生成校准完成信号并发送至上游裸芯发送端,并将校准失败信号calib_fail置1。

[0071]

下游裸芯接收端的校准完成信号calibover_rx由校准成功信号calib_good和校准失败信号calib_fail共同决定,当其中任意一个信号拉高后,calibover_rx就会被自动置1。calibover_rx信号会由od_lane82经第82条lvds通道传输至id_lane82,然后与上游裸芯发送端的calibover_tx信号连接。

[0072]

上游裸芯发送端检测到校准完成信号calibover_tx为高后,自检数据生成器便停止产生自检数据test_data_tx并将自检数据有效信号test_valid_tx置0。然后数据隔离器将允许片内数据流向片间,即不再直接对cpiready置0,而是将其连接到id_lane80,使其上游裸芯片内网络正常感知下游裸芯本地输入通道的工作状况。同时将od_lane1~77连接到cpodata信号、od_lane78连接到cpovalid信号,准备传输上游裸芯片内输出数据。

[0073]

下游裸芯接收端检测到自检数据有效信号test_valid_rx为低后,数据隔离器将允许片间数据流向片内。具体方法为,不再直接对cpivalid置0,而是将其连接到id_lane78,使下游裸芯正常判断片间输入数据是否有效。同时将cpidata连接到id_lane1~77,准备接收片间输入数据。

[0074]

综上所述,本发明通过硬件电路自身实现对各通道对齐状况的检测并进行自动修复,节省了人力和时间资源,同时还能实现较好的校准效果。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1