一种EtherCAT主站及EtherCAT总线系统的制作方法

一种ethercat主站及ethercat总线系统

技术领域

1.本实用新型涉及现场总线技术领域,尤其涉及一种ethercat主站及 ethercat总线系统。

背景技术:

2.如今工业以太网系统已经发展成为了性能相当强大的通信系统,并且在自动化领域中有着越来越重要的作用。实时工业以太网技术ethercat(ethernet forcontrol automation technology)在传统以太网的基础上加以改进,通过processingon the fly、分布时钟同步等技术,具有网络拓扑结构灵活、系统配置简单、通信速率高、实时性好、有效数据率高等的优势,同时接口技术、网关技术等的兼容性问题和速度在使用ethercat之后也已不再是难题,因此ethercat技术在现代工业控制领域有着相当开阔的应用前景。

3.现有的ethercat主站实现的方案主要有两种,一种是基于纯软件操作系统的方案,采用cpu加网卡的体系架构;另一种是基于fpga的纯硬件的方案,基于硬件实现主站。基于操作系统的纯软件方案由于cpu多任务的特性实时性较差,不利于工业领域高精度的控制,同时移植难度较大;而基于fpga的纯硬件主站开发难度较大,开发周期较长,人机交互性较差。

技术实现要素:

4.本实用新型的实施例提供了一种ethercat主站及ethercat总线系统,旨在解决现有的纯软件ethercat主站实时性不高、移植难度大,纯硬件主站开发难度大、周期长及人机交互性较差的问题。

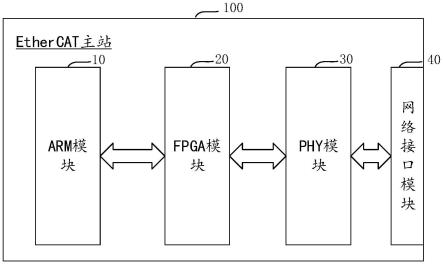

5.本实用新型提供了一种ethercat主站,包括:arm模块、fpga模块、 phy模块以及网络接口模块,arm模块,用于处理ethercat主站的协议和应用层;fpga模块,与所述arm模块连接,所述fpga模块用于数据帧的收发; phy模块,与所述fpga模块连接,所述phy模块用于数据帧的信号转换;网络接口模块,与所述phy模块连接,所述网络接口模块用于与外部通信以进行信号传输。

6.在本实用新型提供的ethercat主站中,所述fpga模块包括cpu接口模块和数据帧收发模块,所述cpu接口模块与所述arm模块连接,所述数据帧收发模块分别与所述cpu接口模块和所述phy模块连接,所述cpu接口模块用于所述arm模块和所述fpga模块之间的数据交互,所述数据帧收发模块用于将所述数据帧按照网络通信协议发送出去以及接收返回的数据帧。

7.在本实用新型提供的ethercat主站中,所述fpga模块还包括发送缓存区,所述发送缓存区连接于所述cpu接口模块和所述数据帧收发模块之间,所述发送缓存区用于缓存所述arm模块传递给所述fpga模块的数据。

8.在本实用新型提供的ethercat主站中,所述fpga模块还包括接收缓存区,所述接收缓存区连接于所述cpu接口模块和所述数据帧收发模块之间,所述接收缓存区用于缓存

所述fpga模块传递给所述arm模块的数据。

9.在本实用新型提供的ethercat主站中,所述fpga模块还包括定时模块,所述定时模块与所述数据帧收发模块连接,所述定时模块用于计时以使所述数据帧收发模块按照固定的时间周期性地发送所述数据帧。

10.在本实用新型提供的ethercat主站中,所述fpga模块还包括时钟同步模块,所述时钟同步模块与所述数据帧收发模块连接,所述时钟同步模块用于同步所述ethercat主站和从站的系统时间。

11.在本实用新型提供的ethercat主站中,所述网络接口模块为rj45网络接口。

12.本实用新型还提供一种ethercat总线系统,包括如上述所述的ethercat 主站。

13.在本实用新型提供的ethercat总线系统中,所述ethercat总线系统还包括从站,所述从站与网络接口模块连接。

14.在本实用新型提供的ethercat总线系统中,所述从站包括参考从站,所述参考从站用于为fpga模块提供参考时钟。

15.本实用新型提供一种ethercat主站及ethercat总线系统,该ethercat主站,包括:arm模块、fpga模块、phy模块以及网络接口模块,arm模块负责ethercat主站的协议驱动和应用层的处理,充分利用arm多任务的特性很好地实现ethercat主站较为复杂的协议驱动和应用,fpga模块负责ethercat主站数据帧的收发,充分利用fpga纯硬件电路干扰较小,实时性较强的特点,很好的提高了主站的实时性,满足工业领域高精度的实时控制要求,本实用新型结合了arm和fpga两者的优势,同时规避了两者的劣势,使得半软半硬主站既有很高的实时性,满足工业控制领域高精度的要求,同时开发难度也较小,开发周期较短,人机交互性较强。

附图说明

16.为了更清楚地说明本实用新型实施例技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

17.图1为本实用新型实施例的ethercat主站的示意图;

18.图2为本实用新型实施例的ethercat主站的fpga模块的示意图;

19.图3为本实用新型实施例ethercat总线系统的示意图。

20.附图标记说明:

21.100、ethercat主站;10、arm模块;20、fpga模块;21、cpu接口模块;22、数据帧收发模块;23、接收缓存区;24、发送缓存区;25、定时模块; 26、时钟同步模块;30、phy模块;40、网络接口模块;200、从站。

具体实施方式

22.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获

得的所有其他实施例,都属于本实用新型保护的范围。

23.本实用新型所提到的方向用语,例如「上」、「下」、「前」、「后」、「左」、「右」、「内」、「外」、「侧面」等,仅是参考附加图式的方向。因此,使用的方向用语是用以说明及理解本实用新型,而非用以限制本实用新型。此外,在附图中,结构相似或相同的结构是以相同标号表示;

24.在本实用新型的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接,还可以是通信连接;可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实用新型中的具体含义。

25.本实用新型实施例通过提供一种ethercat主站及ethercat总线系统,解决了现有的纯软件ethercat主站实时性不高、移植难度大,纯硬件主站开发难度大、周期长及人机交互性较差的问题,通过基于fpga加arm的半软半硬 ethercat主站,结合了arm和fpga两者的优势,同时规避了两者的劣势,使得半软半硬主站既有很高的实时性,满足工业控制领域高精度的要求,同时开发难度也较小,开发周期较短,人机交互性较强。

26.目前的ethercat主站通常是采用纯软件的方案或者是采用纯硬件的方案,其中,对于采用纯软件的方案,使用基于arm的开源linux纯软件主站,ethercat主站的协议和数据收发都在arm核心上完成,由于arm核心多任务调度,导致实时性较差,不满足高精度的控制场景。对于采用纯硬件的方案,使用基于fpga的纯硬件主站,ethercat主站的协议和数据收发都在fpga核心上完成,由于主站的协议较为庞大,导致纯硬件的主站开发难度较大,开发周期较长,人机交互性较差,投入的开发成本较高。

27.本实用新型实施例为解决上述实时性不高和开发难的问题,其技术方案如下:

28.具体的解决思路是,提供一种基于fpga加arm的半软半硬的ethercat 主站,由arm来负责处理ethercat协议和应用,充分利用arm多任务的特性很好地实现ethercat主站较为复杂的协议驱动和应用,由fpga负责处理数据的收发,充分利用fpga纯硬件电路干扰较小,实时性较强的特点,很好的提高了主站的实时性,满足工业领域高精度的实时控制要求,由此,规避了两者的劣势,使得半软半硬主站既有很高的实时性,满足工业控制领域高精度的要求,同时开发难度也较小,开发周期较短,人机交互性较强。

29.为了更好的理解上述技术方案,下面将结合说明书附图以及具体的实施方式对上述技术方案进行详细的说明。

30.参照图1,图1为本实用新型实施例提供的一种ethercat主站100的示意图,该ethercat主站100包括:arm模块10、fpga模块20、phy模块30 以及网络接口模块40,arm模块10,用于处理ethercat主站100的协议和应用层;fpga模块20,与所述arm模块10连接,所述fpga模块20用于数据帧的收发;phy模块30,与所述fpga模块20连接,所述phy模块30用于数据帧的信号转换;网络接口模块40,与所述phy模块30连接,所述网络接口模块40用于与外部通信以进行信号传输。

31.具体地,arm模块10即arm(acorn riscmachine)处理器,在实际应用中,本领域的技术人员可以根据需要选取合适类型的处理器,此处不做限制。 phy模块30,具体为physical layer芯片,简称phy芯片,phy芯片主要的作用是通过通信总线获取ethercat主

站100数据帧,以及将ethercat主站100 数据帧转换为差分信号,然后再发送至ethercat网络中,利用网络接口传输给各ethercat从站200,也即相当于实现数据收发的功能。网络接口模块40具体为rj45网络接口。

32.通过实施本实施例,基于fpga加arm的半软半硬ethercat主站100充分利用两者的优势,综合两者的长处,即解决了纯软件主站实时性不高,移植难度较大的问题,又解决了纯硬件主站开发难度较大,开发周期较长及人机交互性较差的问题。

33.参照图2,在一实施例中,所述fpga模块20(fieldprogrammable gate array,现场可编程门阵列模块)包括cpu接口模块21、数据帧收发模块22、接收缓存区23、发送缓存区24、定时模块25以及时钟同步模块26。在本实施例中,所述cpu接口模块21与所述arm模块10连接,所述数据帧收发模块22与所述 cpu接口模块21和所述phy模块30连接,所述cpu接口用于所述arm模块10和所述fpga模块20之间的数据交互,所述数据帧收发模块22用于将数据帧按照网络通信协议发送出去以及接收返回的数据帧;所述发送缓存区24连接于所述cpu接口模块21和所述数据帧收发模块22之间,所述发送缓存区24 用于缓存所述arm模块10传递给所述fpga模块20的数据;所述接收缓存区 23连接于所述cpu接口模块21和所述数据帧收发模块22之间,所述接收缓存区23用于缓存所述fpga模块20传递给所述arm模块10的数据;所述定时模块25与所述数据帧收发模块22连接,所述定时模块25用于计时以使所述数据帧收发模块22按照固定的时间周期性地发送数据帧;时钟同步模块26,所述时钟同步模块26与所述数据帧收发模块22连接,所述时钟同步模块26用于同步ethercat主站100和从站200的系统时间。其中,通过设置单独的接收缓存区23和发送缓存区24,先将数据缓存起来,可以减轻arm模块10的处理压力,提高数据收发的稳定性和效率。数据帧收发模块22还用于数据帧的校验验证有效数据帧。

34.具体地,所示fpga模块20包括cpu接口模块21、接收缓存区23、发送缓存区24、数据帧收发模块22、定时模块25和时钟同步模块26。其中,所述的cpu接口模块21负责和arm核心对接,用于arm核心和fpga核心之间的数据交互;所述的发送缓存区24用于缓存arm传递给fpga的数据;所述的接收缓存区23用于缓存fpga传递给arm的数据;所述的数据帧收发模块 22将ethercat数据帧按照网络通信协议发送出去同时接收回来;所述的定时模块25负责计时,按照固定的时间周期性地发送ethercat数据帧;所述时钟同步模块26负责同步ethercat主站100和从站200的系统时间,保证具有较高的实时性,满足工业领域需求。

35.在其他实施例中,为了保证ethercat主站100和从站200的时钟同步,除了上述通过时钟同步模块26来实现之外,本实施例还提供一种可选的同步方法。譬如,arm核心的linux操作系统也可以打入xenomai之类的实时补丁,通过 fpga核心和实时补丁共同保证ethercat主站100的实时性。

36.为了体现本实施例ethercat主站100的优势,以下通过本实施例ethercat 主站100数据的收发过程来予以说明。

37.首先fpga模块20通过信号触发arm的中断,该信号是fpga产生的一个普通脉冲信号,arm的中断类型设置为上升沿触发,通过检测这个脉冲信号的上升沿来触发arm中断。当arm模块10收到中断时,按照ethercat主站 100的协议准备相应的数据报并将数据报通过应用接口发送至发送缓存区24,其中,数据报指的是ethercat标准数据报,譬如当主站需要初始化它所控制的从站200时,就发送带有初始化配置数据的ethercat数据报。fpga轮询发

送缓存区24中的数据,然后调用数据帧收发模块22发送数据帧,当ethercat主站100协议还在初始化的阶段时可以直接发送数据帧,当在运行阶段时也就是发送周期性过程数据时,需要调用定时模块25按照设定的周期定时发送数据。数据报经过从站200返回fpga后,fpga调用收发模块接收返回的数据帧,并将数据帧存入接收缓存区23,然后产生一个信号触发arm中断通知arm模块 10取走缓存区中的数据,然后arm根据收到的数据和ethercat主站100协议发送新的数据帧,如此循环,从而实现数据的收发过程。

38.参照图3,本实用新型实施例还提供一种ethercat总线系统,该ethercat 总线系统包括上述实施例所述的ethercat主站100,所述ethercat总线系统还包括从站200,所述从站200与网络接口模块40连接。由于前面说明书已经对该ethercat主站100的架构以及工作原理做了详细地介绍,为了说明书的简洁性,在此不再赘述。

39.在本实施例中,所述从站200包括参考从站200,所述参考从站200用于为 fpga模块20提供参考时钟。具体地,在ethercat总线系统中,包括ethercat 主站100和多个从站200,从站200通过网络接口与ethercat主站100通信连接,从站200中设置有一个参考从站200,该参考从站200是专门用于提供参考时钟来与ethercat主站100进行时钟同步的。具体地,fpga接收从站200返回的数据报,同时fpga调用时钟同步模块26将从站200返回的数据报中解析出参考从站200的系统时间,然后修正fpga的系统时间,使fpga的系统时间和参考时钟保持一致,提高主站的实时性。

40.通过本实施例的ethercat总线系统,基于fpga加arm的半软半硬 ethercat主站100,结合了arm和fpga两者的优势,同时规避了两者的劣势,使得半软半硬主站既有很高的实时性,满足工业控制领域高精度的要求,同时开发难度也较小,开发周期较短,人机交互性较强,同时ethercat主站100和从站200的时间同步在fpga完成。

41.以上所述,仅为本实用新型的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本实用新型的保护范围之内。因此,本实用新型的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1